6 power on configuration – ADLINK cPCI-7249R User Manual

Page 32

24

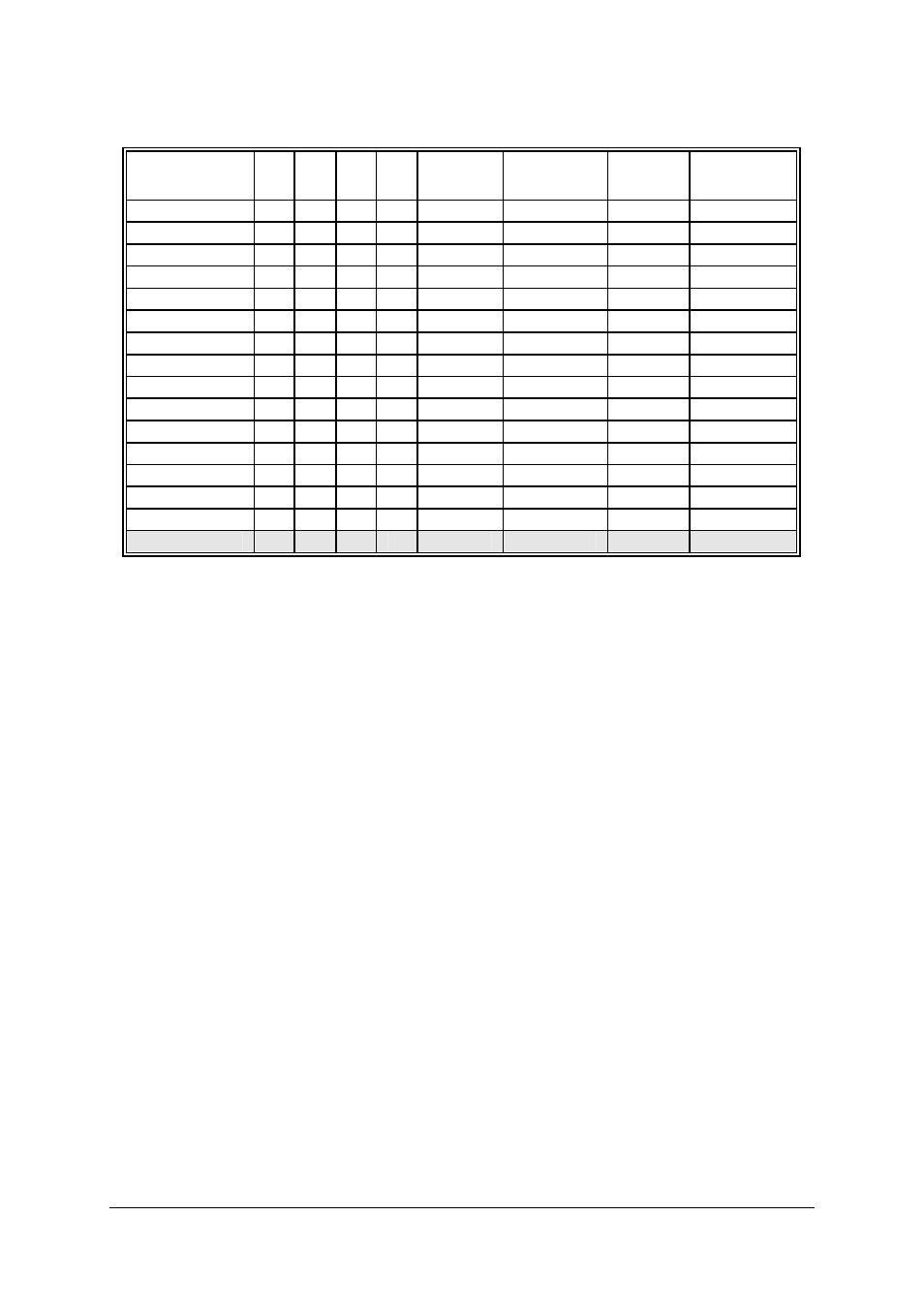

• Operation Theorem

Control

Word

D

4

D

3

D

1

D

0

PORT

A

PORT C

UPPER

PORT

B

PORT C

LOWER

00H

0 0 0 0 O/P

O/P

O/P

O/P

01H

0 0 0 1 O/P

O/P

O/P

I/P

02H

0 0 1 0 O/P

O/P

I/P

O/P

03H

0 0 1 1 O/P

O/P

I/P

I/P

08H

0 1 0 0 O/P

I/P

O/P

O/P

09H

0 1 0 1 O/P

I/P

O/P

I/P

0AH

0 1 1 0 O/P

I/P

I/P

O/P

0BH

0 1 1 1 O/P

I/P

I/P

I/P

10H

1 0 0 0

I/P

O/P

O/P

O/P

11H

1 0 0 1

I/P

O/P

O/P

I/P

12H

1 0 1 0

I/P

O/P

I/P

O/P

13H

1 0 1 1

I/P

O/P

I/P

I/P

18H

1 1 0 0

I/P

I/P

O/P

O/P

19H

1 1 0 1

I/P

I/P

O/P

I/P

1AH

1 1 1 0

I/P

I/P

I/P

O/P

1BH*

1

1

1

1

I/P

I/P

I/P

I/P

Table 4.2 Summary of control word (D0 - D4)

(* power on default configuration)

4.1.6 Power on Configuration

The default configuration after power on, hardware reset or software reset

sets all ports as input ports, therefore the users don’t have to worry about

damaging the external devices when system is power on. In addition, the

default signal level can be pulled high or pulled low by setting the jumpers.

Refer to section 2.7 for setting the power on status of the DIO ports.

4.1.7 Note for Output Data

Be careful of the initial condition of digital output signals. If users set the

control word as output port after power on, the previous uncertain output

value will be put on the output pins immediately. Therefore, BE SURE TO

WRITE A SAFE VALUE TO THE PORTS BEFORE CONFIGURING THEM

AS OUTPUT PORTS.

4.1.8 Note for cPCI-7249R

The PIAE, P1BE, P1CE and P2AE, P2BE, P2CE registers are latched data

from P1A, P1B, P1C and P2A, P2B, P2C respectively. The latch signal is

from the Pin #99 of the 100-pin connector.