3 pxi star trigger, 4 pxi trigger bus, Pxi star trigger pxi trigger bus – ADLINK PXI-2022 User Manual

Page 40: Quirement

32

Function Block and Operation Theory

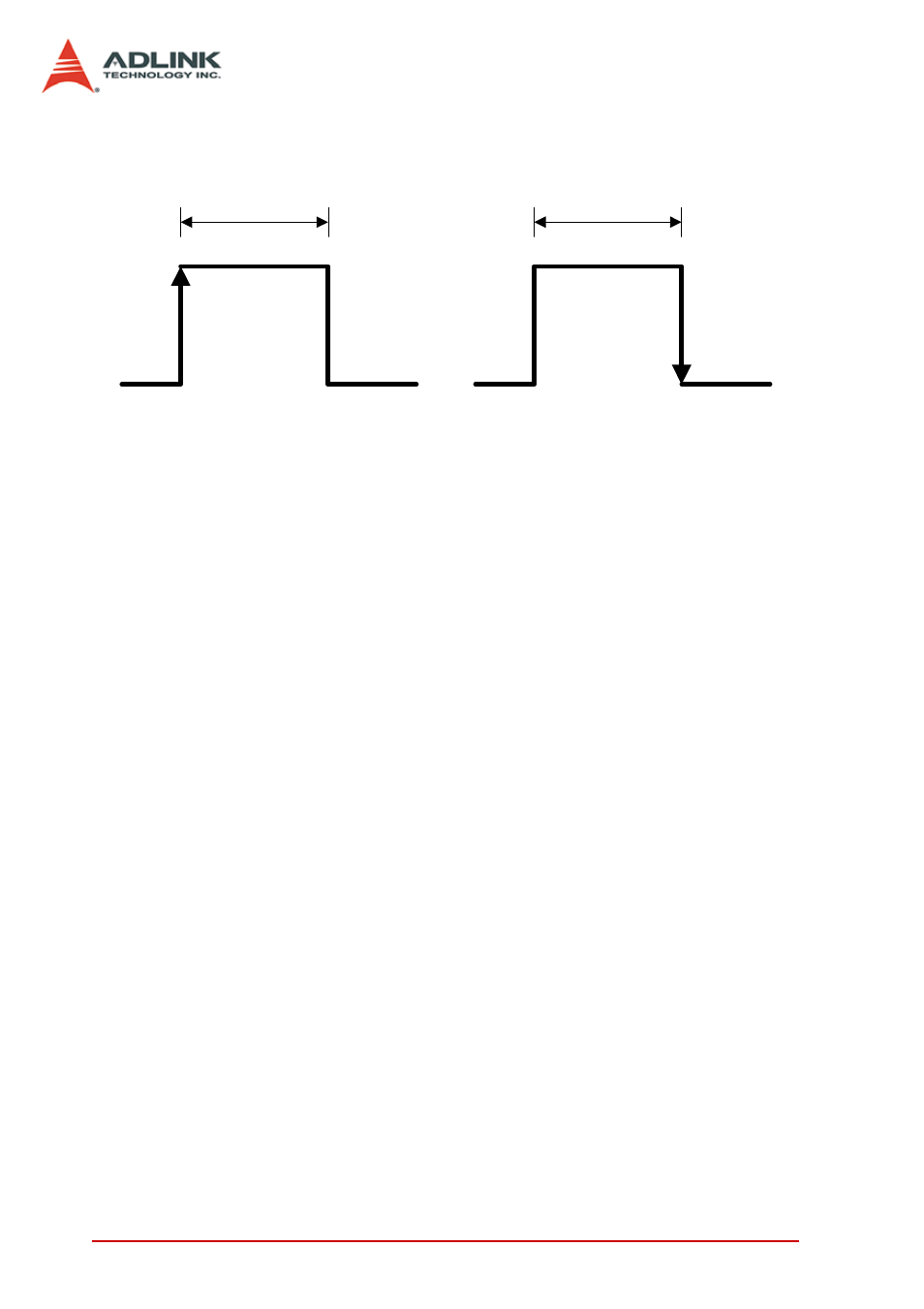

Figure 4-7: External Digital Trigger Polarity and Pulse Width Re-quirement.

4.4.3

PXI Star Trigger

When you select PXI Star Trigger as the trigger source, the PXI-

2020/2022 can accept a TTL-compatible digital signal as a trigger

signal. The trigger occurs when a rising edge or falling edge is

detected at PXI Star Trigger. You can use software to configure the

trigger polarity. The minimum pulse width requirement of this digi-

tal trigger signal is 12.5 ns.

4.4.4

PXI Trigger Bus

The PXI-2020/2022 utilizes PXI Trigger Bus[5] as System Syn-

chronization In-terface (SSI). Using the interconnected bus pro-

vided by PXI Trigger Bus, you can easily synchronize multiple

modules. When configured as input, the PXI-2020/2022 is served

as a slave module and can accept three different SSI signals,

SSI_TIMEBASE (PXI Trigger Bus[0]), PXI Trigger Bus[5] and PXI

Star Trigger Bus[1]. When confi-gured as output, the PXI-2020/

2022 is served as a master module and can output

SSI_TIMEBASE, SSI_AD_TRIG or SSI_ADCONV to PXI Trigger

Bus. Each signal is dedicated routed from the PXI Trigger Bus[5].

Rising edge trigger

event

Falling edge trigger

event

Pulse Width > 12.5 ns

Pulse Width > 12.5 ns