2 ifx_tapi_pcm_if_cfg_t, Ifx_tapi_pcm_if_cfg_t – Maxim Integrated 73M1866B/73M1966B Infineon TAPI High-Level Driver User Manual

Page 27

UG_1x66B_021

73M1866B/73M1966B TAPI High-Level Driver User Guide

Rev. 2.2

27

4.2 IFX_TAPI_PCM_IF_CFG_t

Description

Structure for PCM interface configuration used by IFX_TAPI_PCM_IF_CFG_SET.

Prototype

typedef struct

{

IFX_TAPI_PCM_IF_MODE_t nOpMode;

IFX_TAPI_PCM_IF_DCLFREQ_t nDCLFreq;

IFX_operation_t nDoubleClk;

IFX_TAPI_PCM_IF_SLOPE_t nSlopeTX;

IFX_TAPI_PCM_IF_SLOPE_t nSlopeRX;

IFX_TAPI_PCM_IF_OFFSET_t nOffsetTX;

IFX_TAPI_PCM_IF_OFFSET_t nOffsetRX;

IFX_TAPI_PCM_IF_DRIVE_t nDrive;

IFX_operation_t nShift;

IFX_uint8_t nMCTS;

} IFX_TAPI_PCM_IF_CFG_t;

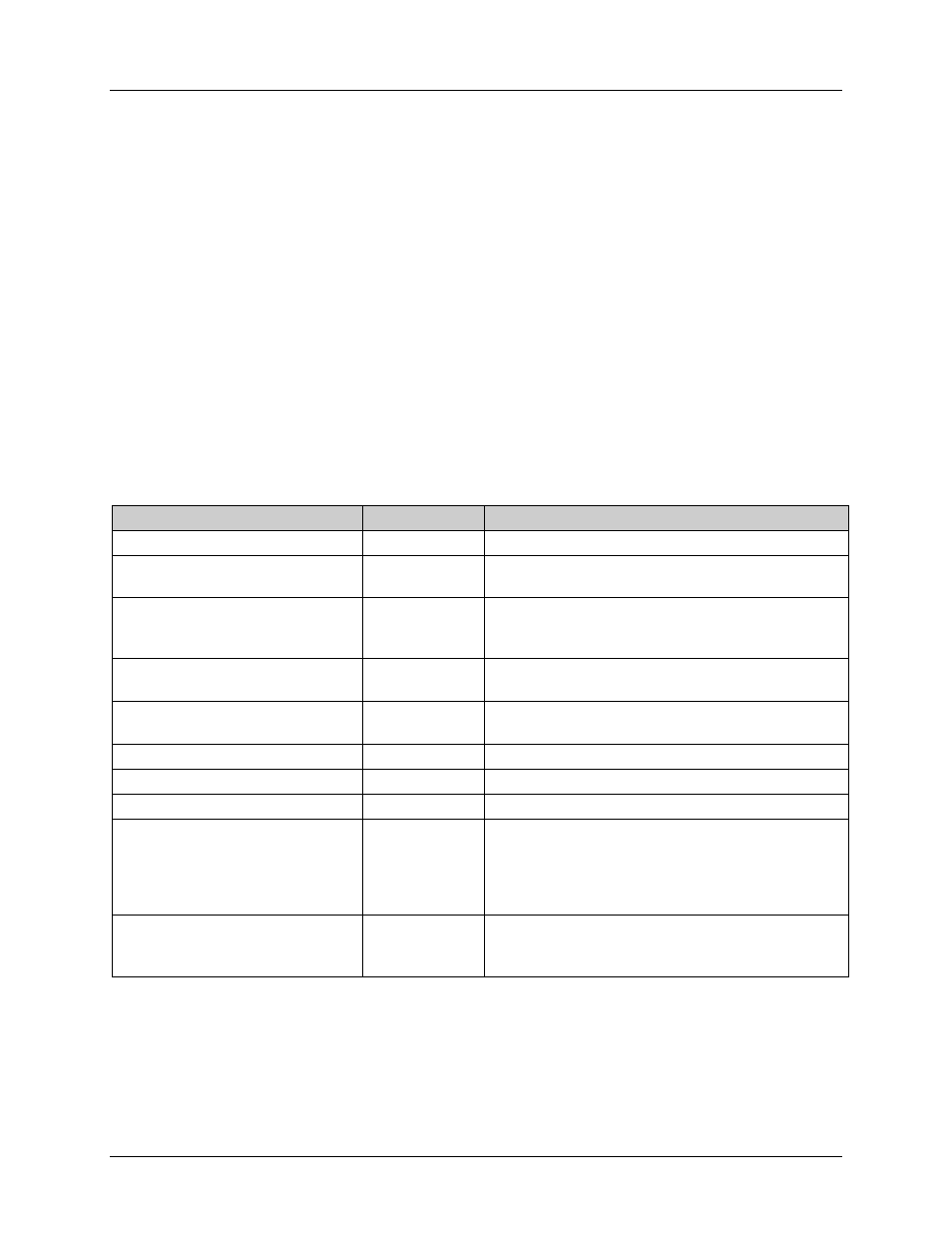

Parameters

Data Type

Name

Description

IFX_TAPI_PCM_IF_MODE_t

nOpMode

PCM interface mode (master or slave mode).

IFX_TAPI_PCM_IF_DCLFREQ_t nDCLFreq

DCL frequency to be used in master and/or slave

mode.

IFX_operation_t

nDoubleClk

Activation/deactivation of the double clock mode.

•IFX_DISABLE: single clocking is used.

•IFX_ENABLE: double clocking is used.

IFX_TAPI_PCM_IF_SLOPE_t

nSlopeTX

Slope to be considered for the PCM transmit

direction.

IFX_TAPI_PCM_IF_SLOPE_t

nSlopeRX

Slope to be considered for the PCM receive

direction.

IFX_TAPI_PCM_IF_OFFSET_t

nOffsetTX

Transmit bit offset.

IFX_TAPI_PCM_IF_OFFSET_t

nOffsetRX

Receive bit offset.

IFX_TAPI_PCM_IF_DRIVE_t

nDrive

Drive mode for bit 0.

IFX_operation_t

nShift

Enable/disable shift access edge.

Shift the access edges by one clock cycle.

• IFX_DISABLE: no shift takes place.

• IFX_ENABLE: shift takes place. Note: This

setting is defined only in double clock mode.

IFX_uint8_t

nMCTS

Reserved.PCM chip specific settings.

Set this field to 0x00 if not advised otherwise by

the IFX support team.