Digital & analog co., ltd. (rev. 1.0) -16 – Calyx S1A0071 - Audio Processor for Class-D Power AMP User Manual

Page 16

S1A0071 Audio Processor for Class-D Power AMP

Digital & Analog Co., Ltd. (Rev. 1.0) -16-

Note 4

The internal gain of S1A0071 is 26dB. (Condition: R1 = R2)

When user wants to get a high gain system, User can do this by changing the values of R1 and R2.

In this case, the Total Gain can be obtained as follows:

26

1

2

20

)

(

+

×

=

R

R

Log

dB

GAINtotal

If the values of R1 and R2 are very high, it will expect the DC offset and if the values of R1 and R2 are

very low, then the THD+N value is high on high power system. By an appropriate R1 and R2 selection,

you can minimize the DC offset and get the good the THD+N characteristics.

Note 5

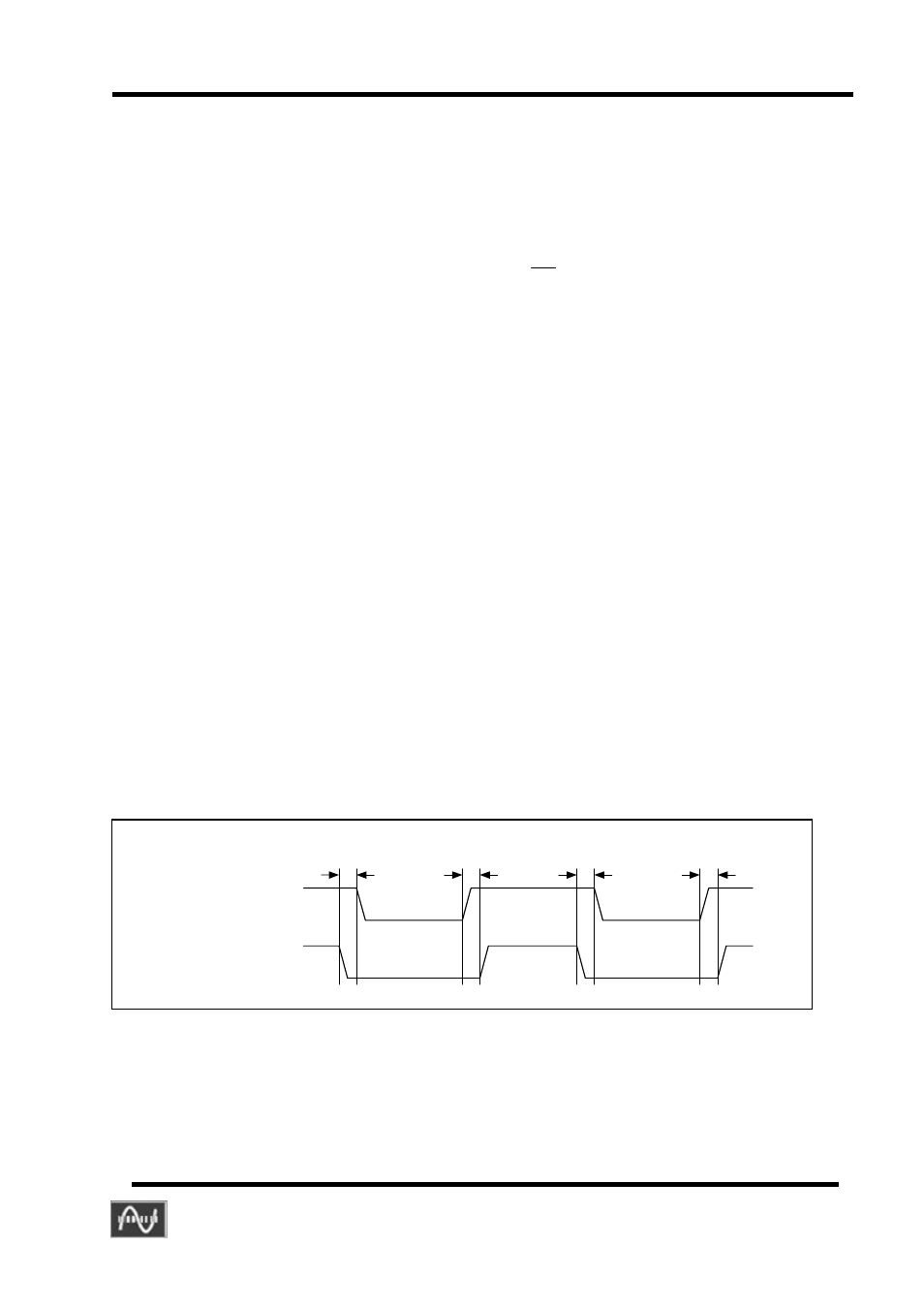

In the application circuit, the resistor Rp connected to the PDCTR and the resistor Rn connected to

NDCTR pins. User can adjust these resistors values to control the ON time delays of P-MOSFET and

N-MOSFET. Because there is a turn-on delay time and rising time and falling time, turn-off delay time

of each MOSFET drive, so user must set the on time delay for each P-MOSFET and N-MOSFET to

prevent arm-short situation. Also more important, the Rp and Rn selection affect the sound quality and

amplifier efficiency, so user should be select appropriate value.

Designed rule of S1A0071, the gate off time minimized and the ON time can be variable so that user

can set the overlap time externally. The PDCTR pin and NDCTR pin voltages are generally set to that

of VB (pin 22) and the flowing current, controlled by the values of Rp and Rn connected externally, can

be used to delay the internal gate ON time. The recommended current range is 10Kohm to 200Kohm,

from which one can select the appropriate current according to the selected output MOSFET and

circuit configuration.

As the resistances increase, ON time is further delayed. Rp and Rn can set the ON time delays of P-

MOSFET and N-MOSFET, respectively.

PMOS Gate Drive

Output (PO)

NMOS Gate Drive

Output(NO)

Tdpo

Tdno

Tdpo

Tdno

Figure 2. Gate Driver on Time Delay