An248 – Cirrus Logic AN248 User Manual

Page 3

AN248

3

•

Note that the same C4 and C6 capacitors may be used.

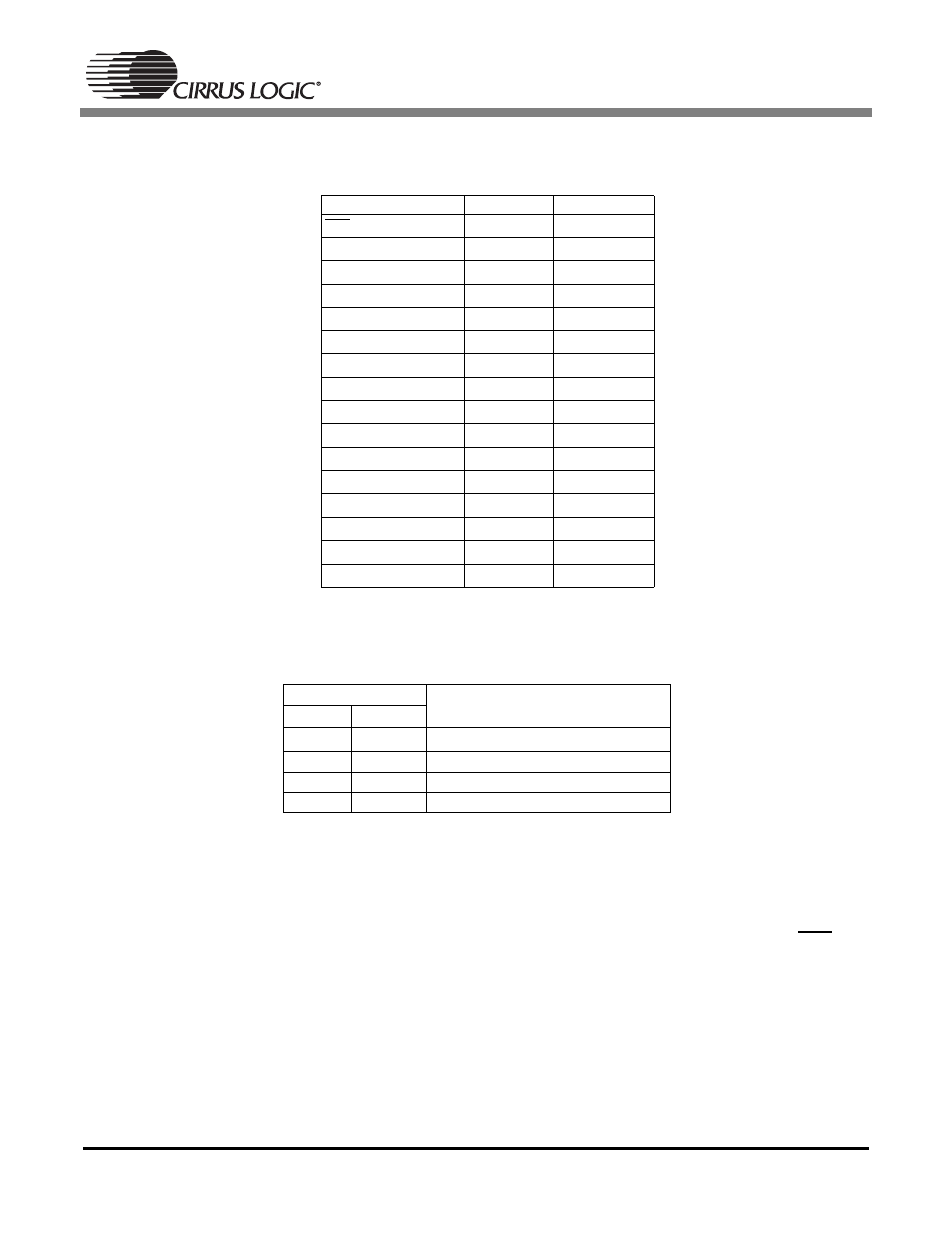

The following table shows the pin for pin mapping between the two part families:

Table 2. CS4334 to CS4344 pin mapping

The part number of the CS4344 family which you will transition to can be determined from the state of

the DIF0 and DIF1 pins as outlined below:

Table 3. CS4340/40A Mode Settings to CS4344 Family Part Numbers

2.1.2

Functional changes

-

The CS4344 family supports de-emphasis through internal SCLK mode. See the CS4344

datasheet for details.

-

The reset state, or power down, is achieved by removing the MCLK signal (instead of the RST pin).

-

The CS4340 MCLK/LRCK ratio of 512x with a 32 kHz sampling rate is not supported by the

CS4344 family. All other MCLK/LRCK ratios and sample rates from the CS4340 are supported. It

is recommended for best performance not to use

Double Speed Mode

with sample rates below

50 kHz, as noted in the CS4344 datasheet.

-

The CS4340A MCLK/LRCK ratios of 512x and 768x with a 32 kHz sampling rate are not supported

by the CS4344. All other MCLK/LRCK ratios and sample rates from the CS4340A are supported.

-

Mute circuit control is not supported by the CS4344 family.

Pin Name

CS4340/40A

CS4344 family

RST

1

SDATA > SDIN

2

1

SCLK > DEM/SCLK

3

2

LRCK

4

3

MCLK

5

4

DIF1

6

DIF0

7

DEM

8

FILT+

9

6

VQ

10

5

REF_GND

11

AOUTB

12

10

AGND

13

8

VA

14

9

AOUTA

15

7

MUTEC

16

CS4340/40A Pin

CS4344 family

Part # and Serial Format Mode

DIF1

DIF0

0

0

CS4344 - I

2

S

0

1

CS4345 - LJ

1

0

CS4346 - RJ24

1

1

CS4348 - RJ16