Cirrus Logic CS2300-03 User Manual

Features, General description, Ordering information

Copyright

© Cirrus Logic, Inc. 2008

(All Rights Reserved)

Advance Product Information

This document contains information for a new product.

Cirrus Logic reserves the right to modify this product without notice.

1x, 4x, 128x, and 256x Clock Multiplier with Internal LCO

Features

Clock Multiplier / Jitter Reduction

–

Generates a Low Jitter 6 - 75 MHz Clock

from a Jittery 23 kHz to 30 MHz Clock

Source

Internal LCO Reference Clock

128 Hz Loop Filter Bandwidth

Selectable Multiplication Factors

–

1x, 4x, 128x, and 256x

Selectable Aux Output Pin

Minimal Board Space Required

–

No External Analog Loop-filter

Components

General Description

The CS2300-03 is an extremely versatile system clock-

ing device that utilizes a programmable phase lock loop.

The CS2300-03 is based on a hybrid analog-digital PLL

architecture comprised of a unique combination of a

Delta-Sigma Fractional-N Frequency Synthesizer and a

Digital PLL. This architecture allows for generation of a

low-jitter clock relative to an external noisy synchroniza-

tion clock with frequencies as low as 23 kHz. The

CS2300-03 is a CS2300-OTP device that has been pre-

configured at the factory. There are three hardware con-

figuration pins available for mode and feature selection.

Ordering Information

The CS2300-03 is available in a 10-pin MSOP package

in Commercial (-10°C to +70°C) grade. Customer de-

velopment kits are also available for custom device

prototyping and device evaluation. Please see

for complete details.

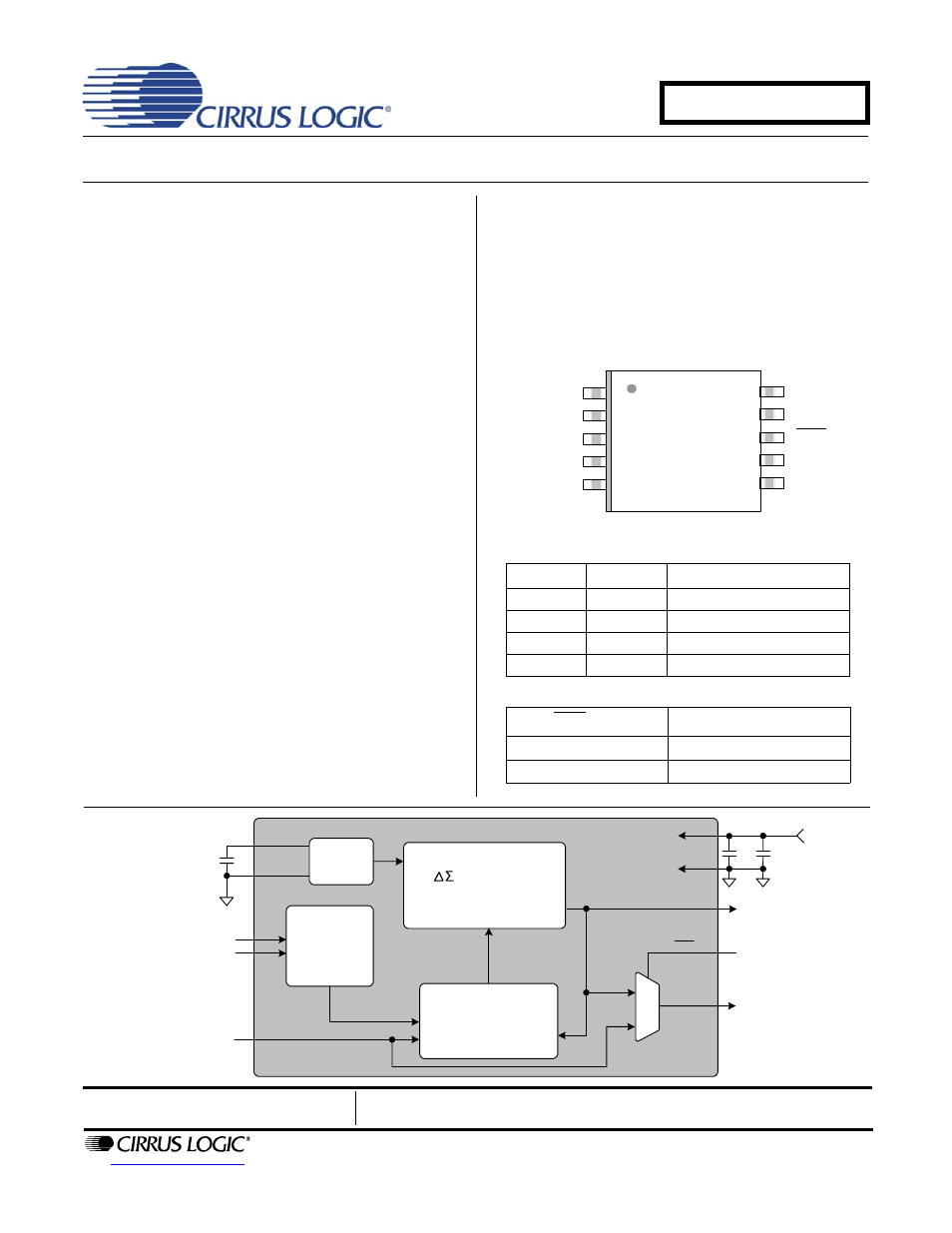

Pin-Out Diagram

Hardware Controls Settings

1

2

3

4

5

6

7

8

9

10

FILTP

PLL_OUT

GND

VD

FILTN

CLK/PLL

M1

M0

AUX_OUT

CLK_IN

M1

M0

PLL_OUT

0

0

1x CLK_IN

0

1

4x CLK_IN

1

0

128x CLK_IN

1

1

256x CLK_IN

CKL/PLL

AUX_OUT Source

0

CLK_IN

1

PLL_OUT

6 MHz to 75 MHz

PLL Output

3.3 V

Fractional-N

Frequency Synthesizer

128 Hz BW Digital PLL

& Fractional N Logic

Output to Input

Clock Ratio

N

23 kHz to 30 MHz

Frequency Reference

LCO

M[1:0]

00=1x

01=4x

10=128x

11=256x

Ratio Selection

AUX Output

Source Select

FILTP

FILTN

0.1 µF

CLK_IN

M1

M0

CLK/PLL

VD

0.1 µF

1 µF

GND

PLL_OUT

23 kHz to 75 MHz

AUX Output

PLL_OUT

CLK_IN

AUX_OUT

February '08

PS856A1

CS2300-03