3 enable pll clock output on unlock (clkoutunl), 4 m2 pin configuration (m2config[2:0]), Cs2200-otp – Cirrus Logic CS2200-OTP User Manual

Page 19

CS2200-OTP

DS842F2

19

6.3.3

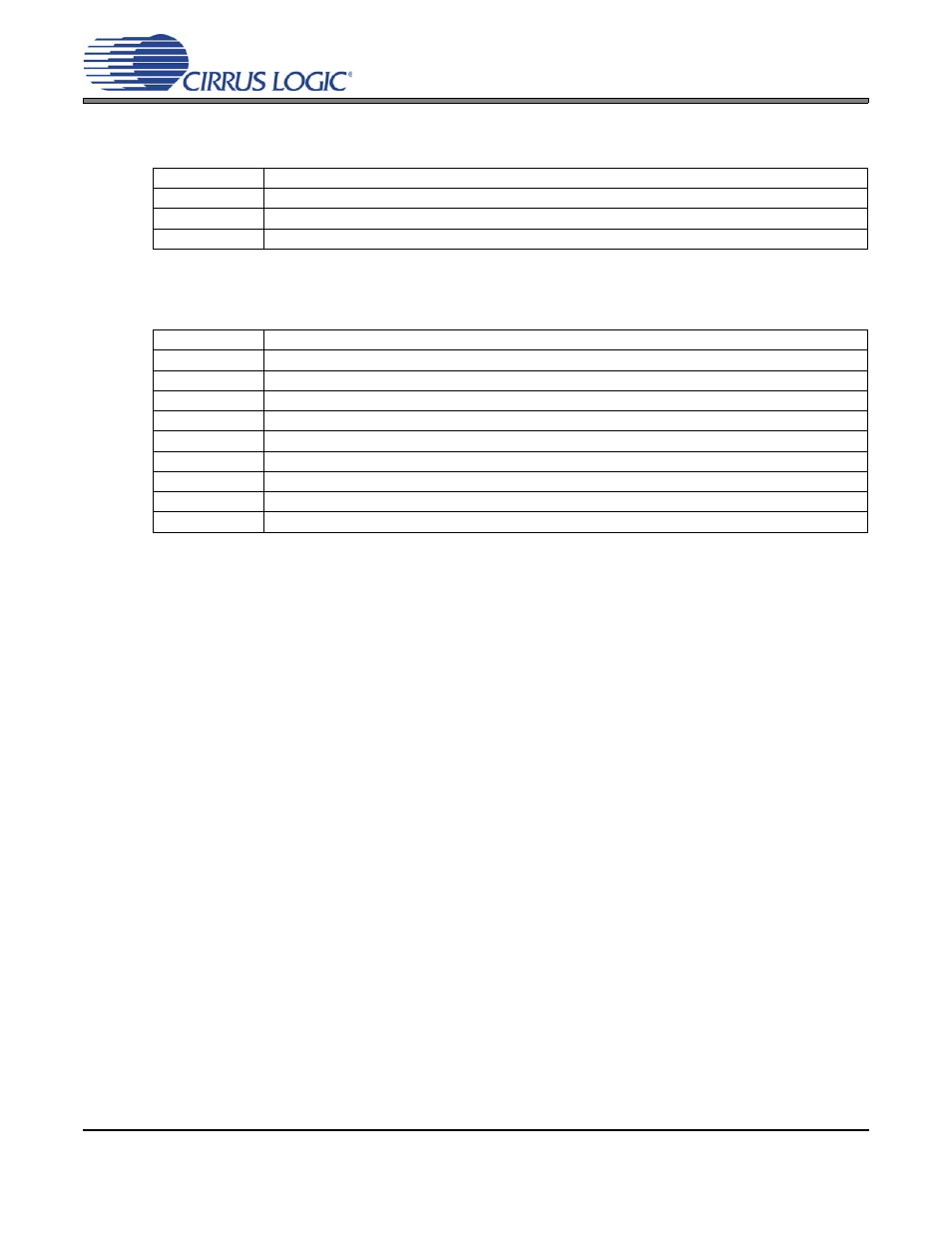

Enable PLL Clock Output on Unlock (ClkOutUnl)

Defines the state of the PLL output during the PLL unlock condition.

6.3.4

M2 Pin Configuration (M2Config[2:0])

Controls which special function is mapped to the M2 pin

.

ClkOutUnl

Clock Output Enable Status

0

Clock outputs are driven ‘low’ when PLL is unlocked.

1

Clock outputs are always enabled (results in unpredictable output when PLL is unlocked).

Application:

“PLL Clock Output” on page 13

M2Config[2:0]

M2 pin function

000

Disable CLK_OUT pin.

001

Disable AUX_OUT pin.

010

Disable CLK_OUT and AUX_OUT.

011

RModSel[1:0] Modal Parameter Enable.

100

Reserved.

101

Reserved.

110

Reserved.

111

Force AuxOutSrc[1:0] = 10 (PLL Clock Out).

Application:

“M2 Mode Pin Functionality” on page 15

See also other documents in the category Cirrus Logic Hardware:

- CobraNet (147 pages)

- CS4961xx (54 pages)

- CS150x (8 pages)

- CS1501 (16 pages)

- CS1601 (2 pages)

- CS1601 (16 pages)

- CS1610 (16 pages)

- CRD1610-8W (24 pages)

- CRD1611-8W (25 pages)

- CDB1610-8W (21 pages)

- CS1610A (18 pages)

- CDB1611-8W (21 pages)

- CDB1610A-8W (21 pages)

- CDB1611A-8W (21 pages)

- CRD1610A-8W (24 pages)

- CRD1611A-8W (25 pages)

- CS1615 (16 pages)

- AN403 (15 pages)

- AN401 (14 pages)

- AN400 (15 pages)

- AN375 (27 pages)

- AN376 (9 pages)

- CRD1615-8W (22 pages)

- CRD1616-8W (23 pages)

- AN402 (14 pages)

- AN404 (15 pages)

- CRD1615A-8W (21 pages)

- CS1615A (16 pages)

- CS1630 (56 pages)

- AN374 (35 pages)

- AN368 (80 pages)

- CRD1630-10W (24 pages)

- CRD1631-10W (25 pages)

- CS1680 (16 pages)

- AN405 (13 pages)

- AN379 (31 pages)

- CRD1680-7W (31 pages)

- AN335 (10 pages)

- AN334 (6 pages)

- AN312 (14 pages)

- AN Integrating CobraNet into Audio Products (16 pages)

- CobraNet Audio Routing Primer (9 pages)

- Bundle Assignments in CobraNet Systems (3 pages)

- CS2300-01 (3 pages)

- CS2000-CP (38 pages)