Timing, Status byte, Checksum – Vaisala HMM105 User Manual

Page 11

Chapter 2 _______________________________________________________________ I2C Interface

VAISALA _____________________________________________________________________ 9

Timing

The minimum time delay that the master must wait between the invoke

and response messages depends on the operation. If the operation

includes a write to the non-volatile memory, it takes more time than other

operations.

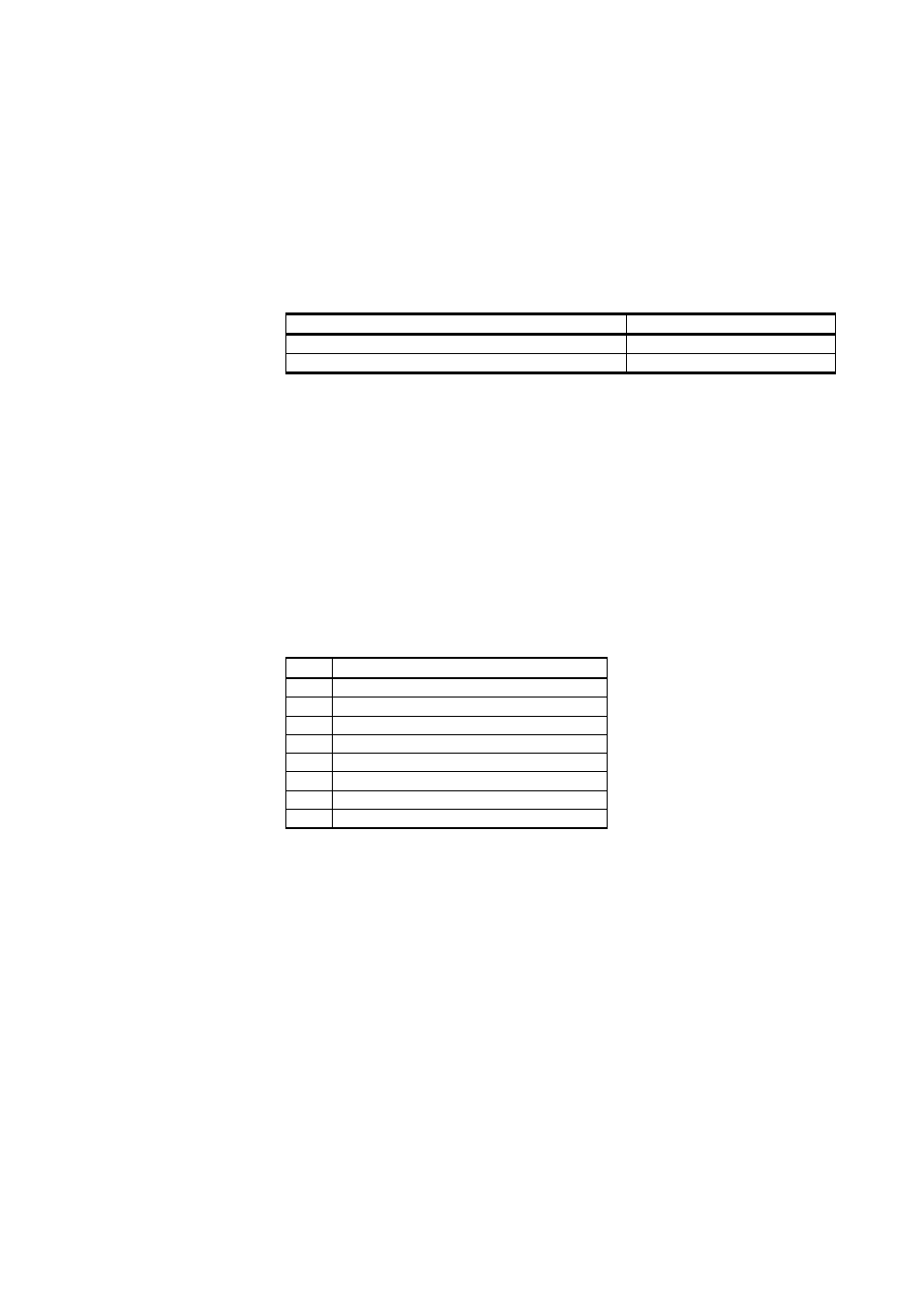

Table 8

Timing

Operation

Minimum delay

Normal delay between invoke and response

10 ms

Delay when write to non-volatile memory

300 ms

Status Byte

The status byte gives the master device information about the slave

device’s state, and information about the communication status with the

ACK/NACK bit.

The status byte has bits for signaling Status, Warning, Error and Critical

error statuses. These bits are cleared when the status word is read. Bits

are set when the corresponding status or error state changes in the slave

device.

Table 9

Status Byte

Bit# Description

0

ACK/NACK

1

Critical error

2

Error

3

Warning

4

Status

5

6

7

Checksum

HMM105 uses a CRC16-CCITT checksum in its protocol frame. CCITT

(x.25) polynomial is X

16

+X

12

+X

5

+1 = 11021h. Initial value is 0000h and

the final value is XORed with FFFFh. The checksum uses a bit reversed

algorithm.

When the invoke message is received, the checksum is calculated using

bytes from the command byte to the last byte of the data field. The

checksum needs to be valid before data can be accepted. If the checksum

is not valid, the message is rejected and the internal state of the GMP231

is set to Idle.

When the response message is transmitted, the checksum is calculated

using bytes from the status byte to the last byte of the data field.