Asus A8N-VM CSM User Manual

Page 62

2 - 2 2

2 - 2 2

2 - 2 2

2 - 2 2

2 - 2 2

C h a p t e r 2 : B I O S s e t u p

C h a p t e r 2 : B I O S s e t u p

C h a p t e r 2 : B I O S s e t u p

C h a p t e r 2 : B I O S s e t u p

C h a p t e r 2 : B I O S s e t u p

D R A M S C R U B R E D I R E C T [ D i s a b l e d ]

D R A M S C R U B R E D I R E C T [ D i s a b l e d ]

D R A M S C R U B R E D I R E C T [ D i s a b l e d ]

D R A M S C R U B R E D I R E C T [ D i s a b l e d ]

D R A M S C R U B R E D I R E C T [ D i s a b l e d ]

Allows you to enable or disable DRAM scrub redirect, which

allows the system to correct DRAM ECC errors immediately

when they occur, even if background scrubbing is on.

Configuration options: [Disabled] [Enabled]

D R A M B G S c r u b [ D i s a b l e d ]

D R A M B G S c r u b [ D i s a b l e d ]

D R A M B G S c r u b [ D i s a b l e d ]

D R A M B G S c r u b [ D i s a b l e d ]

D R A M B G S c r u b [ D i s a b l e d ]

Allows DRAM scrubbing to correct memory errors so later

reads are correct. Doing this while memory is not being used

improves performance. Configuration options: [Disabled]

[40ns] [80ns] [160ns] [320ns] [640ns] [1.28us] [2.56us]

[5.12us] [10.2us] [20.5 us] [41.0us] [81.9us] [163.8us]

[327.7us] [655.4us] [1.31ms] [2.62ms] [5.24ms]

[10.49ms] [20.97ms] [42.00ms] [84.00ms]

L 2 C a c h e B G S c r u b [ D i s a b l e d ]

L 2 C a c h e B G S c r u b [ D i s a b l e d ]

L 2 C a c h e B G S c r u b [ D i s a b l e d ]

L 2 C a c h e B G S c r u b [ D i s a b l e d ]

L 2 C a c h e B G S c r u b [ D i s a b l e d ]

Allows the L2 Data Cache RAM to be corrected while idle.

Configuration options: [Disabled] [40ns] [80ns] [160ns] [320ns]

[640ns] [1.28us] [2.56us] [5.12us] [10.2us] [20.5 us] [41.0us]

[81.9us] [163.8us] [327.7us] [655.4us] [1.31ms] [2.62ms]

[5.24ms] [10.49ms] [20.97ms] [42.00ms] [84.00ms]

D a t a C a c h e B G S c r u b [ D i s a b l e d ]

D a t a C a c h e B G S c r u b [ D i s a b l e d ]

D a t a C a c h e B G S c r u b [ D i s a b l e d ]

D a t a C a c h e B G S c r u b [ D i s a b l e d ]

D a t a C a c h e B G S c r u b [ D i s a b l e d ]

Allows the L1 Data Cache RAM to be corrected while idle.

Configuration options: [Disabled] [40ns] [80ns] [160ns] [320ns]

[640ns] [1.28us] [2.56us] [5.12us] [10.2us] [20.5 us] [41.0us]

[81.9us] [163.8us] [327.7us] [655.4us] [1.31ms] [2.62ms]

[5.24ms] [10.49ms] [20.97ms] [42.00ms] [84.00ms]

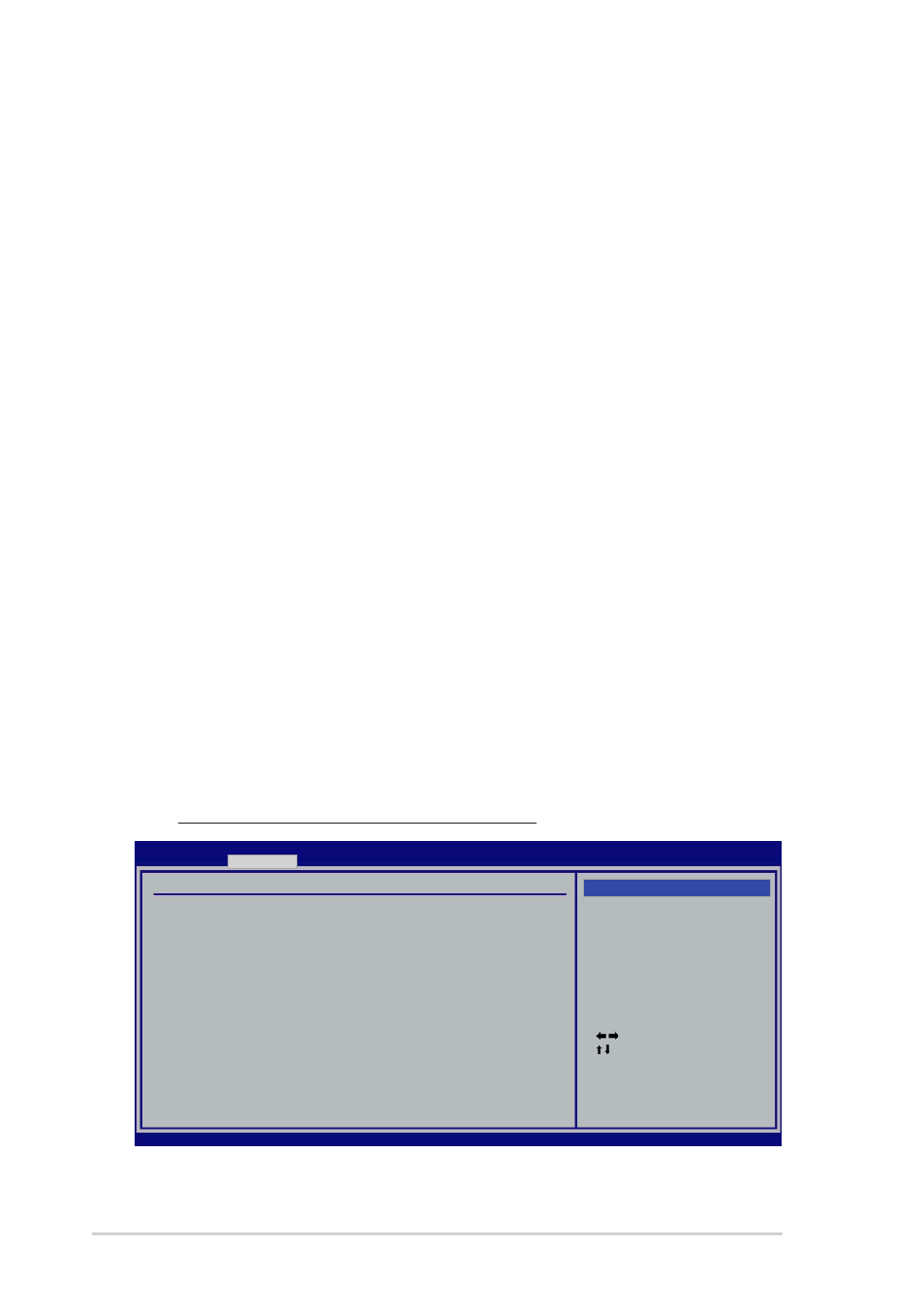

NvigpBridge/C51PV Chipset Configuration

Select Screen

Select Item

+- Change Option

F1

General Help

F10 Save and Exit

ESC Exit

v02.58 (C)Copyright 1985-2004, American Megatrends, Inc.

Advanced

NvigpBridge/C51PV Chipset Configuration

Primary Graphics Adapter

[[PCI -> PCI Express]

OnChip VGA Frame Buffer Size

[64 MB]

OnChip VGA Trap Enable

[Disabled]

Options

PCI -> PCI Express -> IGP

IGP -> PCI Express -> PCI