2 chipset configuration, Chipset configuration -17, Cpu bridge chipset configuration – Asus RS520-E6/RS8 User Manual

Page 77: C3 auto demotion [enabled, Scroll down for more items

ASUS RS520-E6/RS8

5-17

5.4.2

Chipset Configuration

The Chipset configuration menu allows you to change advanced chipset settings.

Select an item then press

C3 Auto Demotion [Enabled]

When enabled, CPU will conditionally demote C6/C7 requests to C3 based on on-

core auto-demote information.

Configuration options: [Disabled] [Enabled]

v02.61 (C)Copyright 1985-2008, American Megatrends, Inc.

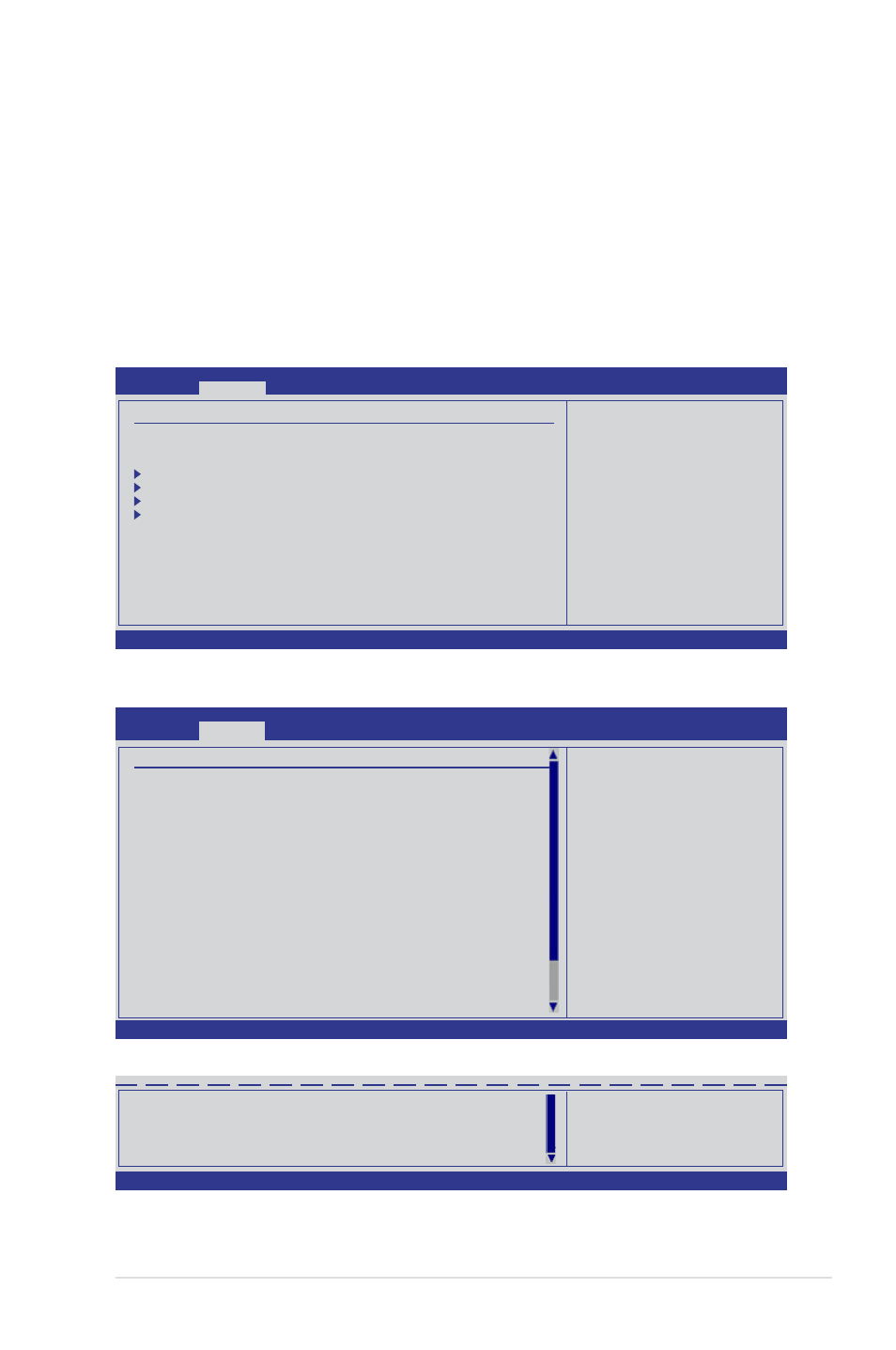

BIOS SETUP UTILITY

Advanced

Advanced Chipset Settings

WARNING: Setting wrong values in below sections

may cause system to malfunction.

CPU Bridge Configuration

North Bridge Configuration

South Bridge Configuration

Intel VT-d Configuration

←→

Select Screen

↑↓

Select Item

Enter Go to Sub Screen

F1 General Help

F10 Save and Exit

ESC Exit

Configure North Bridge

features.

CPU Bridge Chipset Configuration

v02.61 (C)Copyright 1985-2008, American Megatrends, Inc.

BIOS SETUP UTILITY

Advanced

CPU Bridge Chipset Configuration

CPU REVISION

:B0

Current CSI Frequency

:6.400GT

Current Memory Frequency

:1066 Mhz

CSI Links Speed

[Full-Speed]

CSI Frequency

[Auto]

CSI Isochronous

[Disabled]

CSI L0s

[Disabled]

CIS L1

[Disabled]

Memory Frequency

[Auto]

Memory Mode

[Independent]

Memory ECC Function

[Enabled]

Double Rate Refresh

[Auto]

Demand Scrubbing

[Disabled]

Patrol Scrubbing

[Disabled]

NUMA Aware

[Auto]

Page Policy

[Closed]

←→

Select Screen

↑↓

Select Item

+- Change Option

F1 General Help

F10 Save and Exit

ESC Exit

To transition the CSI

links to full-speed

or leave them in

slow-mode.

v02.61 (C)Copyright 1985-2008, American Megatrends, Inc.

Scroll down for more items.

Adaptive Page

[Disabled]

Data Scramble

[Enabled]

Split Below 4GB

[Disabled]

Channel Interleaving

[6:1]

Rank Interleaving

[4:1]