Single-supply, low-power, serial 8-bit adcs, Detailed description, Pin description – Rainbow Electronics MAX1116 User Manual

Page 6

MAX1115/MAX1116

Detailed Description

The MAX1115/MAX1116 ADCs use a successive-

approximation conversion technique and input

track/hold (T/H) circuitry to convert an analog signal to

an 8-bit digital output. The SPI/QSPI/MICROWIRE com-

patible interface directly connects to microprocessors

(µP’s) without additional circuitry (Figure 3).

Track/Hold

The input architecture of the ADC is illustrated in the

equivalent-input circuit shown in Figure 4 and is com-

posed of the T/H, input multiplexer, input comparator,

switched capacitor DAC, and autozero rail.

The acquisition interval begins with the falling edge of

CNVST. During the acquisition interval, the analog input

(CH0) is connected to the hold capacitor (C

HOLD

).

Once the acquisition is complete, the T/H switch opens

and C

HOLD

is connected to GND, which retains the

charge on C

HOLD

as a sample of the signal at the ana-

log input.

Sufficiently low source impedance is required to ensure

an accurate sample. A source impedance of <1.5k

Ω is

recommended for accurate sample settling. A 100pF

capacitor at the ADC inputs will also improve the accu-

racy of an input sample.

Conversion Process

The MAX1115/MAX1116 conversion process is internal-

ly timed. The total acquisition and conversion process

takes <7.5µs. Once an input sample has been

acquired, the comparator’s negative input is then con-

nected to an autozero supply. Since the device

requires only a single supply, the negative input of the

comparator is set to equal V

DD

/2. The capacitive DAC

restores the positive input to V

DD

/2 within the limits of 8-

bit resolution. This action is equivalent to transferring a

charge Q

IN

= 16pF

✕

V

IN

from C

HOLD

to the binary-

weighted capacitive DAC, which forms a digital repre-

sentation of the analog-input signal.

Single-Supply, Low-Power, Serial 8-Bit ADCs

6

_______________________________________________________________________________________

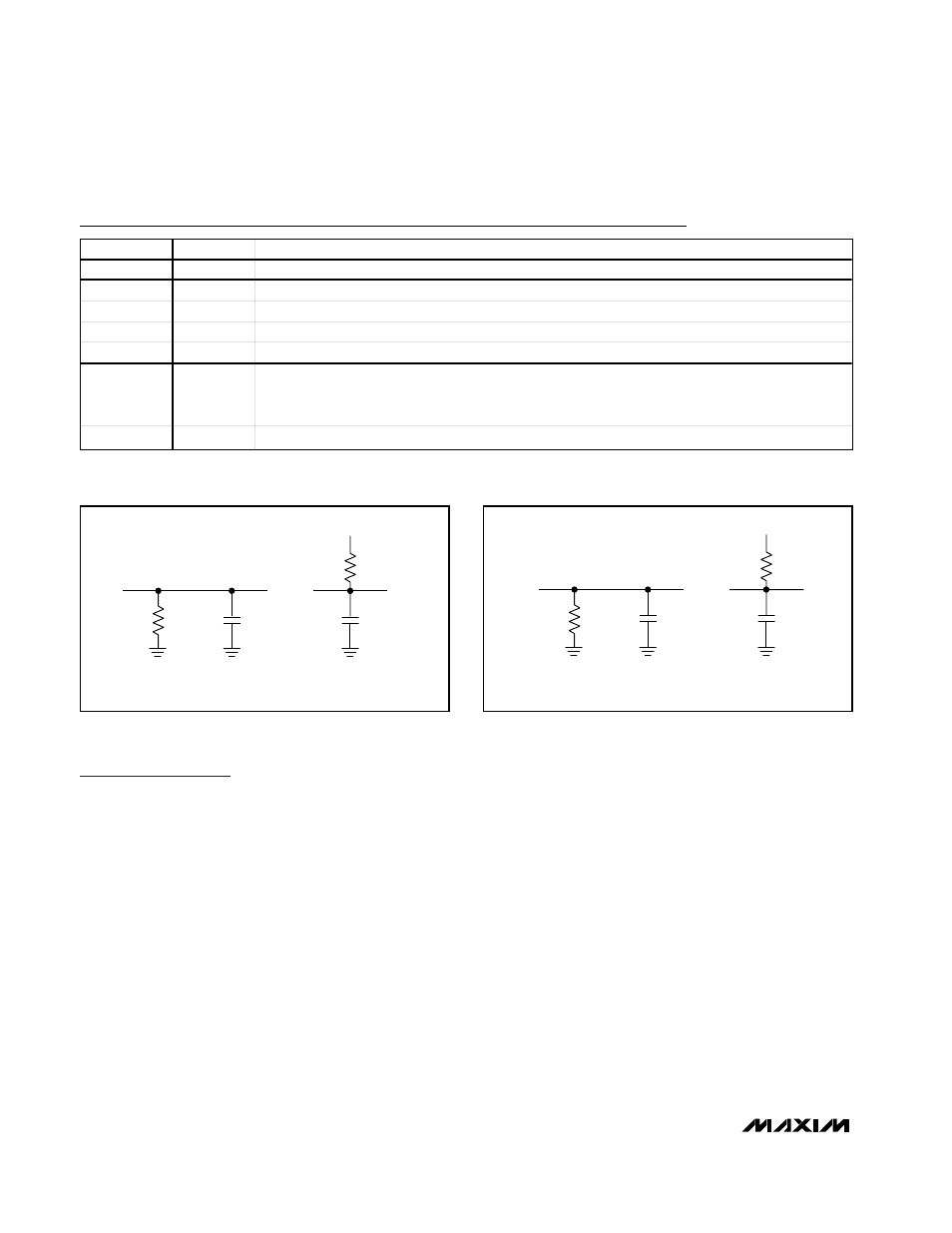

Pin Description

PIN

NAME

FUNCTION

1

V

DD

Positive Supply Voltage

2

CH0

Analog Voltage Input

3, 5

I.C.

Internally Connected. Connect to ground.

4

GND

Ground

6

CNVST

Convert/Start Input. CNVST initiates a power-up and starts a conversion on its falling edge.

7

DOUT

Serial Data Output. Data is clocked out on the falling edge of SCLK. DOUT goes low at the start of a

conversion and presents the MSB at the completion of a conversion. DOUT goes high impedance

once data has been fully clocked out.

8

SCLK

Serial Clock. Used for clocking out data on DOUT.

V

DD

3k

Ω

C

LOAD

GND

DOUT

C

LOAD

GND

3k

Ω

DOUT

a) V

OL

TO V

OH

b) HIGH-Z TO V

OL

AND V

OH

to V

OL

V

DD

3k

Ω

C

LOAD

GND

DOUT

C

LOAD

GND

3k

Ω

DOUT

a) V

OH

TO High-Z

b) V

OL

TO HIGH-Z

Figure 1. Load Circuits for Enable Time

Figure 2. Load Circuits for Disable Time