2 register 75h: fan spin-up mode, 23 undefined registers, 0 xor test mode – Rainbow Electronics LM85 User Manual

Page 24: 0 differences between the lm85bimq and lm85cimq, Functional description

Functional Description

(Continued)

23.14

1944

420

30.04

2523

420

38.16

3205

420

47.06

3953

420

61.38

5156

420

94.12

7906

420

This register is not effected when the Ready/Lock/Start/Override register Lock bit is set. After power up the default value is used

whenever the Ready/Lock/Start/Override register Start bit is cleared even though modifications to this register are possible.

4.22.2 Register 75h: Fan Spin-up Mode

Register

Address

Read/

Write

Register

Name

Bit 7

(MSB)

Bit 6 Bit 5 Bit 4 Bit 3

Bit 2

Bit 1

Bit 0

(LSB)

Default

Value

Lock?

75h

R/W

Fan Spin-up Mode

RES

RES

RES

RES

RES

PWM3 SU PWM2 SU PWM1 SU

7h

U

The PWM SU bit configures the PWM spin-up mode. If PWM SU is cleared the spin-up time will terminate after time programmed

by the Fan Configuration register has elapsed. When set to a 1, the spin-up time will terminate early if the TACH reading exceeds

the Tach Minimum value or after the time programmed by the Fan Configuration register has elapsed, whichever occurs first.

This register becomes Read Only when the Ready/Lock/Start/Override register Lock bit is set. Any further attempts to write to this

register shall have no effect. After power up the default value is used whenever the Ready/Lock/Start/Override register Start bit

is cleared even though modifications to this register are possible.

4.23 Undefined Registers

Any reads to undefined registers will always return 00h. Writes to undefined registers will have no effect and will not return an

error.

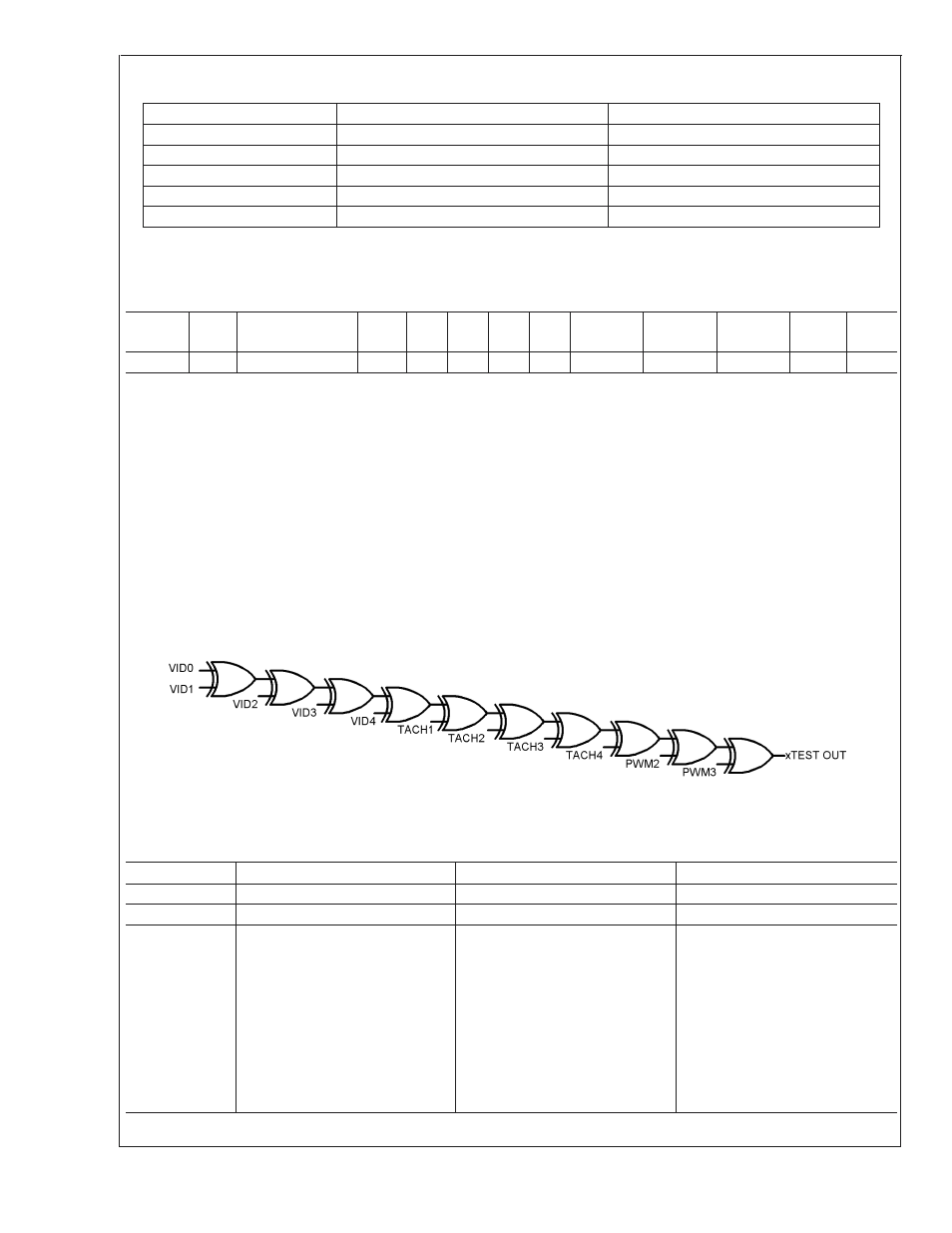

5.0 XOR TEST MODE

The LM85 incorporates a XOR tree test mode. When the test mode is enabled by setting the “XEN” bit high in the Test Register

at address 6Fh via the SMBus, the part will enter XOR test mode.

Since the test mode an XOR tree, the order of the signals in the tree is not important. SMBDAT and SMBCLK are not to be

included in the test tree.

20035308

6.0 DIFFERENCES BETWEEN THE LM85BIMQ AND LM85CIMQ

It is highly recommended that new designs use the LM85BIMQ.

Item No.

Description

LM85CIMQ

LM85BIMQ

1

Voltage Monitoring Accuracy

+3.5% to −0.5% of Full Scale

±

2% of Full Scale

2

PWM Output logic LOW loading

3mA at 0.4V

8mA at 0.4V

3

LSB and MSB Fan TACH value

registers (registers 28h, 29h; 2Ah,

2Bh; 2Ch, 2Dh; 2Eh, 2Fh)

Tach value registers must be read

LSB followed by MSB. Reading the

LSB latches the MSB. For example:

if you read the LSB then the MSB,

subsequent reads of just the MSB

register will yield the old result.

Internally, the TACH result is being

updated but there is no read access

unless the LSB register is read

before an MSB.

Tach value registers must be read

LSB followed by MSB. Reading the

LSB latches the MSB until read.

After the MSB is read it will be

updated with a new value, without

requiring a read of the LSB register.

LM85

www.national.com

24