8 register 41h: interrupt status register 1, Functional description – Rainbow Electronics LM85 User Manual

Page 13

Functional Description

(Continued)

Bit

Name

R/W

Default

Description

1

LOCK

R/W

0

Setting this bit to 1 locks specified limit and parameter registers. Once this bit

is set, limit and parameter registers become read only and will remain locked

until the device is powered off. This register bit becomes read only once it is

set.

2

READY

R

0

The LM85 sets this bit automatically after the part is fully powered up, has

completed the power-up-reset process, and after all A/D converters are

properly functioning.

3

OVRID

R/W

If this bit is set to 1, all PWM outputs will go to 100% duty cycle regardless of

whether or not the lock bit is set. For the LM85C only, when a PWM is

programmed in the disabled mode (Fan Configuration registers 5C-5Eh, bits

fan_config[7:5] = ZON[2:0]=100) the PWM stays in the disabled mode for this

case. Override bit works in all other cases (zone1-3, hottest ...). For the

LM85B the OVRID bit has precedence over the disabled mode. Therefore,

when OVRID is set the PWM will go to 100% even if the PWM is in the

disabled mode.

4–7

Reserved

R

0

Reserved

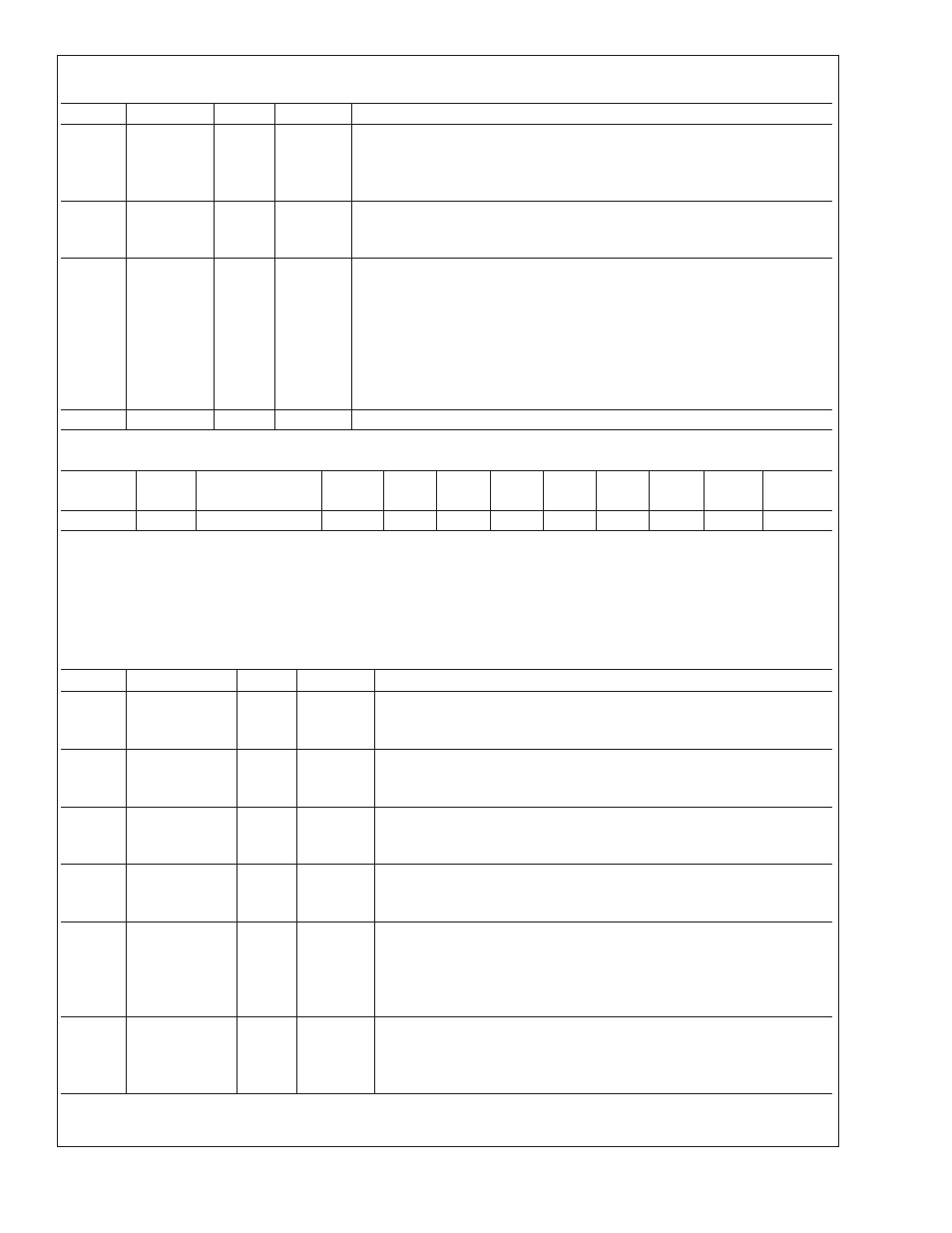

4.8 Register 41h: Interrupt Status Register 1

Register

Address

Read/

Write

Register

Name

Bit 7

(MSB)

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

(LSB)

Default

Value

41h

R

Interrupt Status 1

ERR

ZN3

ZN2

ZN1

5V

3.3V

V

CCP

2.5V

00h

The Interrupt Status Register 1 bits will be automatically set, by the LM85, whenever a fault condition is detected. A fault condition

is detected whenever a measured value is outside the window set by its limit registers. ZN3 and ZN1 bits will be set when a diode

fault condition, such as a disconect or short, is detected. More than one fault may be indicated in the interrupt register when read.

This register will hold a set bit(s) until the event is read by software. The contents of this register will be cleared (set to 0)

automatically by the LM85 after it is read by software, if the fault condition is no longer exists. Once set, the Interrupt Status

Register 1 bits will remain set until a read event occurs, even if the fault condition no longer exists

This register is read only — a write to this register has no effect.

Bit

Name

R/W

Default

Description

0

2.5V_Error

R

0

The LM85 automatically sets this bit to 1 when the 2.5V input voltage is

less than or equal to the limit set in the 2.5V Low Limit register or greater

than the limit set in the 2.5V High Limit register.

1

V

CCP

_Error

R

0

The LM85 automatically sets this bit to 1 when the V

CCP

input voltage is

less than or equal to the limit set in the V

CCP

Low Limit register or greater

than the limit set in the V

CCP

High Limit register.

2

3.3V_Error

R

0

The LM85 automatically sets this bit to 1 when the 3.3V input voltage is

less than or equal to the limit set in the 3.3V Low Limit register or greater

than the limit set in the 3.3V High Limit register.

3

5V_Error

R

0

The LM85 automatically sets this bit to 1 when the 5V input voltage is less

than or equal to the limit set in the 5V Low Limit register or greater than

the limit set in the 5V High Limit register.

4

Zone 1 Limit

Exceeded

R

0

The LM85 automatically sets this bit to 1 when the temperature input

measured by the Remote1− and Remote1+ inputs is less than or equal to

the limit set in the Processor (Zone1) Low Temp register or more than the

limit set in the Processor (Zone1) High Temp register. This bit will be set

when a diode fault is detected.

5

Zone 2 Limit

Exceeded

R

0

The LM85 automatically sets this bit to 1 when the temperature input

measured by the internal temperature sensor is less than or equal to the

limit set in the Internal (Zone2) Low Temp register or greater than the limit

set in the Internal (Zone2) High Temp register.

LM85

www.national.com

13