Rainbow Electronics MAX768 User Manual

Page 8

MAX768

Low-Noise, Dual-Output, Regulated Charge Pump

for GaAsFET, LCD, and VCO Supplies

8

_______________________________________________________________________________________

Shutdown

The MAX768 has two active-low, TTL logic-level shut-

down inputs:

PSHDN and NSHDN. When both inputs

are pulled low, the MAX768 shuts down and the supply

current is reduced to 10µA max over temperature.

Pulling

PSHDN low turns off the positive linear regula-

tor; the doubler charge pump remains active. Pulling

the

NSHDN input low while PSHDN remains high turns

off the inverter charge pump, the negative linear regula-

tor, and the output-ready indicator (Table 1).

Capacitors

The overall dropout voltage is a function of the charge

pump’s output resistance and the voltage drop across

the linear regulator. The charge-pump output resistance

is a function of the switching frequency and the capaci-

tor’s ESR value. Therefore, minimizing the charge-pump

capacitors’ ESR minimizes dropout voltage.

See Table 2 for capacitor selection. All capacitors

should be either surface-mount ceramic chip or tanta-

lum. External capacitor values may be adjusted to opti-

mize size, performance, and cost.

PSHDN

Positive output active

1

1

POUT

STATUS

NSHDN

Negative output active

NOUT

STATUS

0.8

SUPPLY

CURRENT

(mA)

Negative output inactive

0.7

Positive output active

0

1

Negative output active

0.3

Shutdown (low-power mode)

0.0001

Shutdown (low-power mode)

0

0

Positive output inactive

1

0

100

IN

20 to 240

External Clock

SYNC

INPUT

25

GND

FREQUENCY

(kHz)

2.2µF

10µF

C = 220µF/f (kHz)

10µF

4.7µF

CAPACITORS

C1, C2, C3, C4

C5, C6

C7

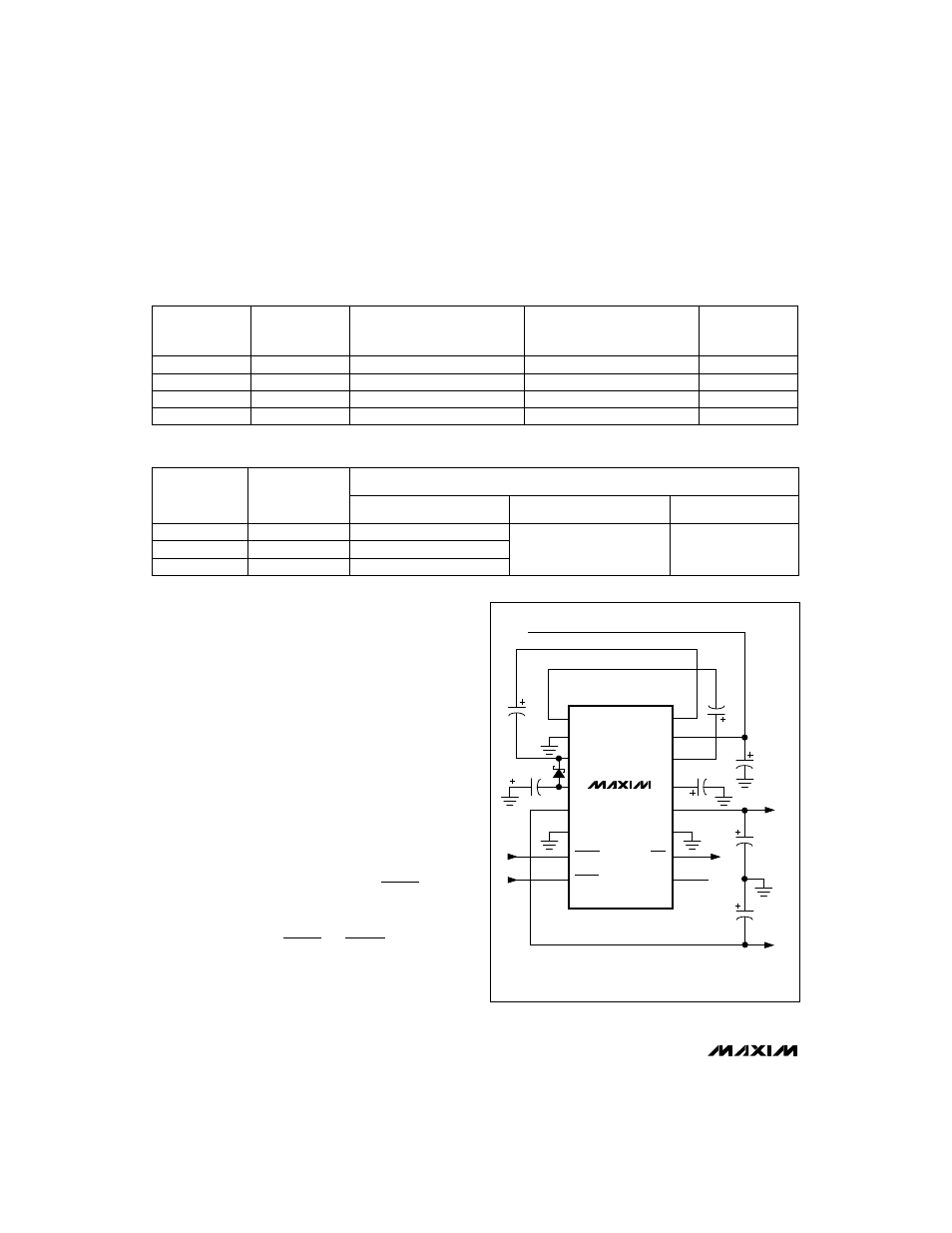

Figure 2. MAX768 Standard Application Circuit

Table 1. Shutdown-Control Logic

Table 2. Charge-Pump Capacitor Selection

(Figure 2)

MAX768

C1-

GND

C4

C3

C2

C1

C7

C5

C6

C2-

V-

NOUT

SETN

NSHDN

PSHDN

SEE TABLE 2 FOR CAPACITOR VALUES

C2+

V

IN

TO

V

IN

-5V

+5V

IN

C1+

V+

POUT

SETP

RDY

SYNC

R

84

8 C1

C3

2

f

C1

R

84

8 C1

4 C2

(C4

)

2

f

C1

1

f

C2

POUT

ESR

ESR

OSC

NOUT

ESR

ESR

ESR

OSC

OSC

=

+

(

)

+

(

)

+

=

+

(

)

+

(

)

+

+

+