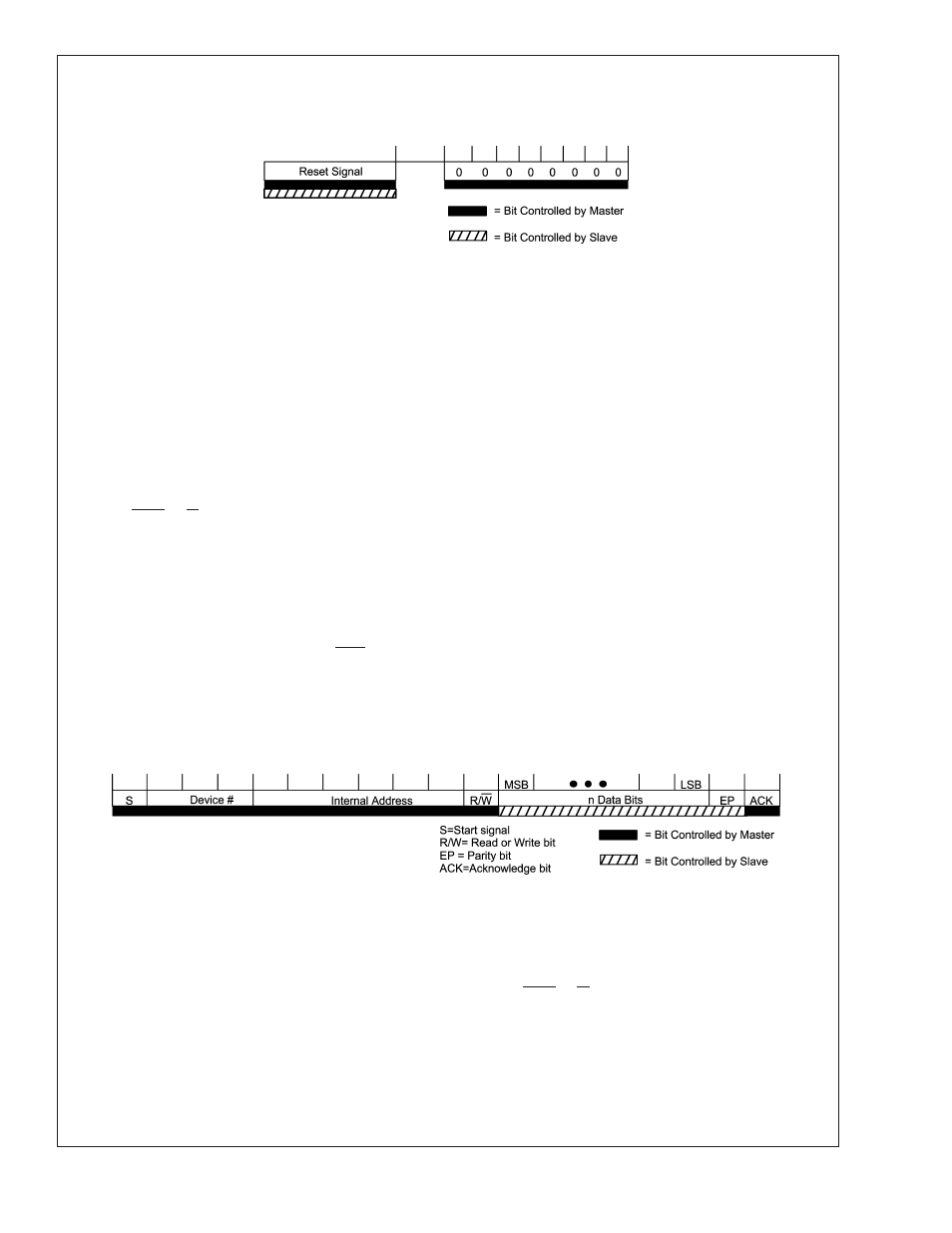

Figure 4. bus reset transaction, 2 read transaction, 3 write transaction – Rainbow Electronics LM32 User Manual

Page 11: 0 functional description

1.0 Functional Description

(Continued)

1.3.2 Read Transaction

During a read transaction, the master reads data from a

register at a specified address within a slave. A read trans-

action begins with a Start Bit and ends with an ACK bit, as

shown in Figure 5.

•

Device Number This is the address of the LM32 device

accessed. Address "000" is a broadcast address and can

be responded to by all the slave devices. The LM32

ignores the broadcast address during a read transaction.

•

Internal Address The address of a register within the

LM32 that is read.

•

Read/Write (R/W) A "1" indicates a read transaction.

•

Data Bits During a read transaction the data bits are

driven by the LM32. Data is transferred serially with the

most significant bit first. This allows throughput optimiza-

tion based on the information that needs to be read.

The LM32 supports 8-bit or 16-bit data fields, as de-

scribed in Section 2.0 "Register Set".

•

Even Parity (EP) This bit is based on all preceding bits

(device number, internal address, Read/Write and data

bits) and the parity bit itself. The parity -number of 1’s - of

all the preceding bits and the parity bit must be even - i.e.,

the result must be 0. During a read transaction, the EP bit

is sent by the LM32 to the master to allow the master to

check the received data before using it.

•

Acknowledge (ACK) During a read transaction the ACK

bit is sent by the master indicating that the EP bit was

received and was found to be correct, when compared to

the data preceding it, and that no conflict was detected

on the bus (excluding Attention Request - see Section

1.3.5 "Attention Request Transaction"). A read transfer is

considered "complete" only when the ACK bit is received.

A transaction that was not positively acknowledged is not

considered "complete" by the LM32 and following are

performed:

— The BER bit in the LM32 Device Status register is set

— The LM32 generates an Attention Request before, or

together with the Start Bit of the next transaction

A transaction that was not positively acknowledged is

also not considered "complete" by the master (i.e. inter-

nal operations related to the transaction are not per-

formed). The transaction may be repeated by the master,

after detecting the source of the Attention Request (the

LM32 that has a set BER bit in the Device Status regis-

ter). Note that the SensorPath protocol neither forces, nor

automates re-execution of the transaction by the master.

The values of the ACK bit are:

— 1: Data was received correctly

— 0: An error was detected (no-acknowledge).

1.3.3 Write Transaction

In a write transaction, the master writes data to a register at

a specified address in the LM32. A write transaction begins

with a Start Bit and ends with an ACK Data Bit, as show in

Figure 6.

•

Device Number This is the address of the slave device

accessed. Address "000" is a broadcast address and is

responded to by all the slave devices. The LM32 re-

sponds to broadcast messages to the Device Control

Register.

•

Internal Address This is the register address in the

LM32 that will be written.

•

Read/Write (R/W) A "0" data bit directs a write transac-

tion.

20071108

FIGURE 4. Bus Reset Transaction

20071109

FIGURE 5. Read Transaction, master reads data from LM32

LM32

www.national.com

11