Pin description (continued) – Rainbow Electronics MAX5043 User Manual

Page 11

______________________________________________________________________________________

11

MAX5042/MAX5043

Two-Switch Power ICs with Integrated

Power MOSFETs and Hot-Swap Controller

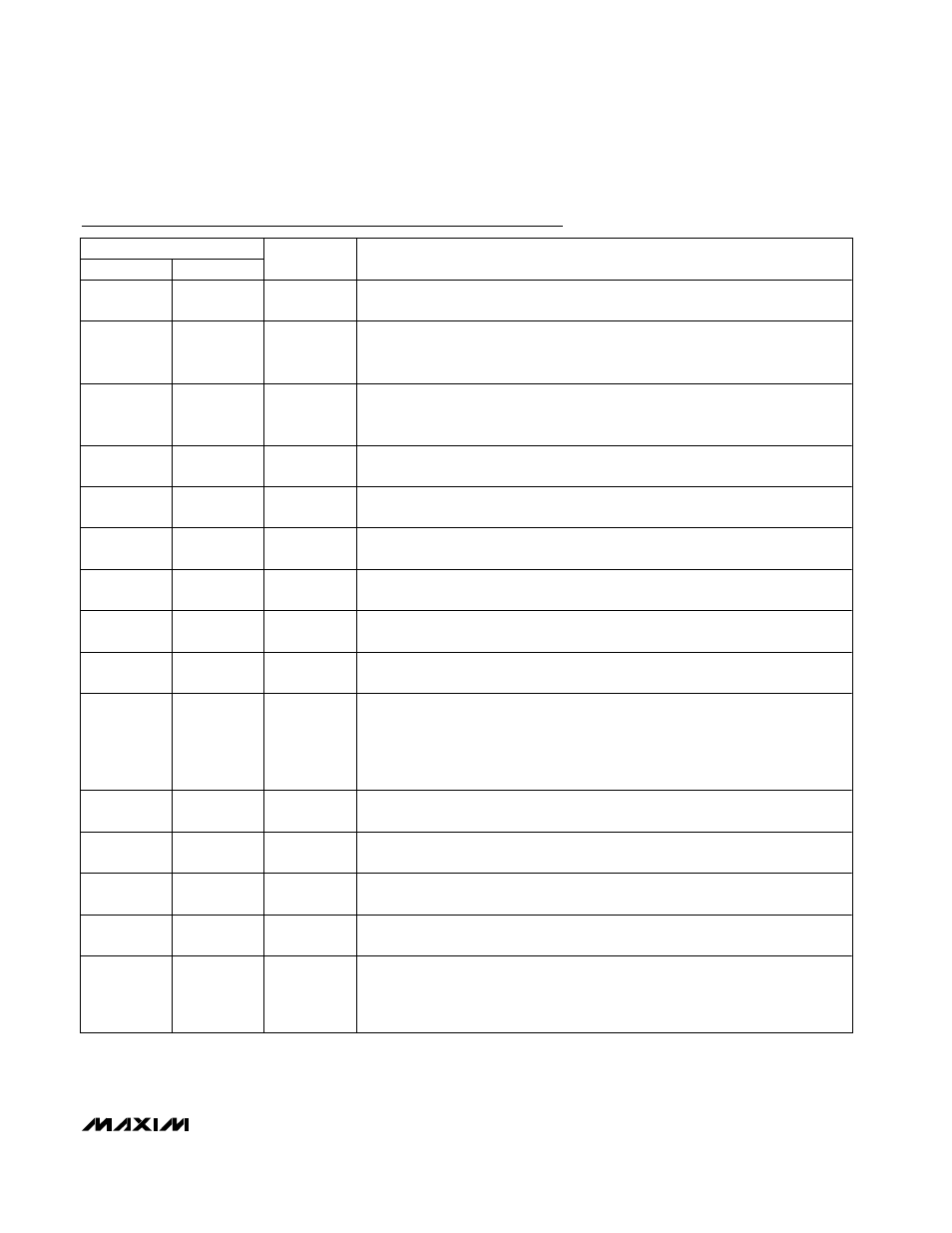

Pin Description (continued)

PIN

MAX5042

MAX5043

NAME

FUNCTION

26

—

HSOK

Hot-Swap OK (MAX5042 Only). HSOK’s open-drain output is forced to NEGIN upon

hot-swap completion.

27

—

HSEN

Hot-Swap Enable (MAX5042 Only). HSEN is the center point of the internal hot-swap

UVLO divider. Use an external voltage-divider or a 100k

Ω

pullup resistor to the most

positive rail to override.

28, 29

—

NEGIN

Negative Supply Input (MAX5042 Only). NEGIN connects to the most negative input

supply rail. NEGIN provides the hot-swap circuit’s most negative connection. NEGIN

is at the same potential as the IC substrate.

30

—

HSGATE

Hot-Swap Gate (MAX5042 Only). Connect HSGATE to the gate of the external hot-

swap MOSFET.

31

—

HSDRAIN

Hot-Swap MOSFET Drain Sense (MAX5042 Only). Connect HSDRAIN to the drain of

the external hot-swap MOSFET.

32

32

CSOUT

Current-Sense Amplifier Output. The amplifier has a gain of 10. Connect CSOUT to

RAMP for current-mode control.

33

33

CSP

Positive Current-Sense Connection. Place the current-sense resistor as close as

possible to the device and use a Kelvin connection.

34

34

CSN

Negative Current-Sense Connection. Place the current-sense resistor as close as

possible to the device and use a Kelvin connection.

35

26, 28, 29,

31, 35

PWMNEG

Analog Signal Return for the PWM Section

36

36

DRVDEL

Driver Delay Adjust Connection. Connect a resistor and a 0.22µF capacitor from

DRVDEL to PWMNEG. The resistor at DRVDEL controls the skew between the

PPWM signal and the power pulse applied to the internal power MOSFETs. Use in

conjunction with a secondary-side synchronous-rectifier controller. The skew allows

for the optimization of the synchronous-rectifier drive pulse.

37

37

PPWM

PWM Pulse Output. PPWM leads the internal power MOSFET pulse by an amount

determined with the resistor value at DRVDEL.

38

38

REG9

9V Internal Regulator Output. Use primarily as a source for the internal gate drivers.

Bypass REG9 to PWMNEG with a 1µF ceramic capacitor.

39

39

REG5

5V Internal Regulator Output. Bypass REG5 to PWMNEG with a 1µF ceramic

capacitor.

41

41

REG15

15V Startup Regulator Output. A voltage greater than 18V on REG15 disables the

regulator. Bypass REG15 to PWMNEG with at least one 1µF ceramic capacitor.

46

46

UVLO

PWM Undervoltage Lockout. UVLO is the center point of the PWM undervoltage

lockout divider. Use an external divider or a 100k

Ω

pullup resistor to POSINPWM to

override. Connect the external resistor-divider network from POSINPWM to

PWMNEG.