Pin description, Detailed description – Rainbow Electronics MAX5100 User Manual

Page 6

MAX5100

+2.7V to +5.5V, Low-Power, Quad, Parallel

8-Bit DAC with Rail-to-Rail Voltage Outputs

6

_______________________________________________________________________________________

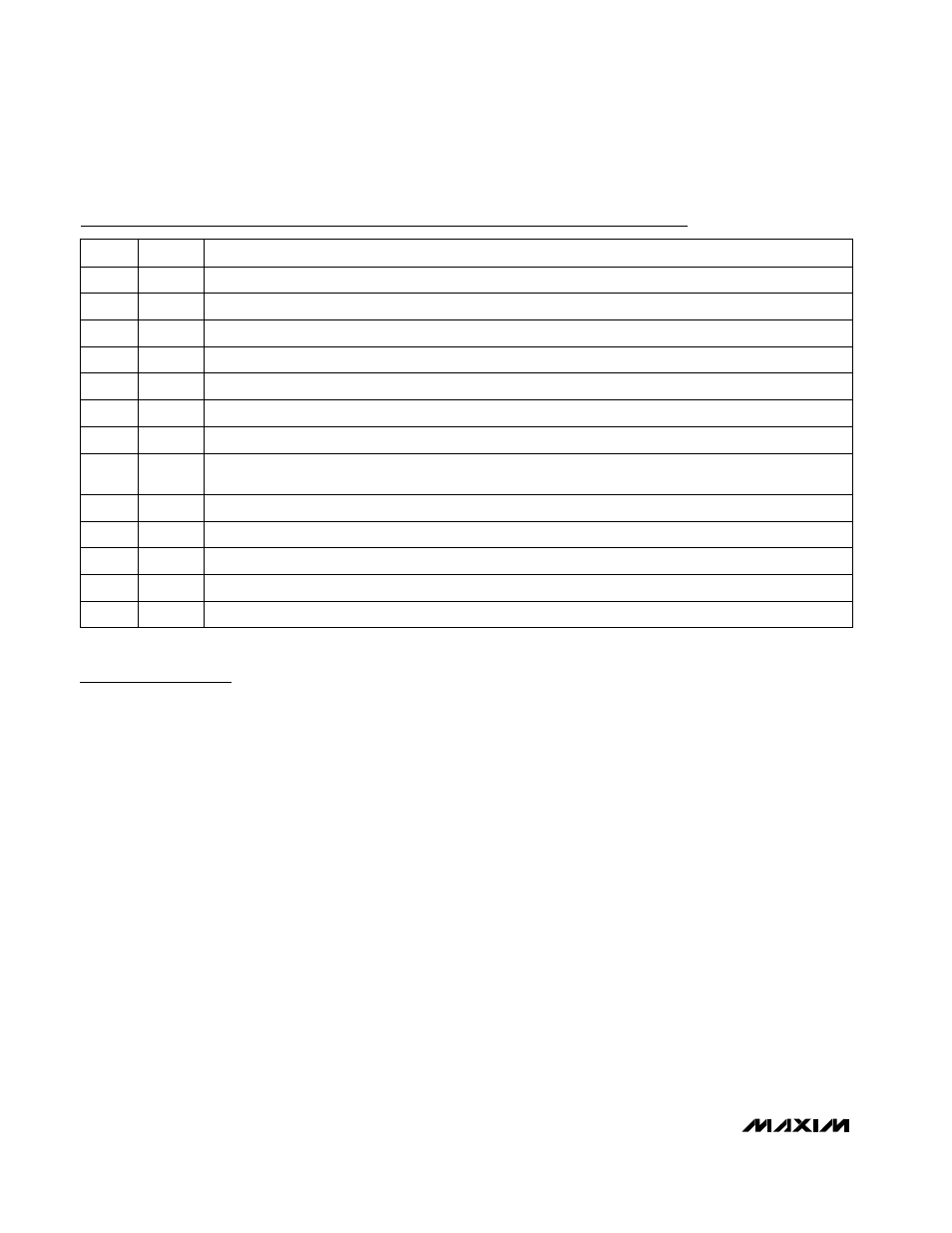

Pin Description

DAC Address Select Bit (MSB)

A1

16

Shutdown. Connect SHDN to GND for normal operation.

SHDN

5

Write Input (active low). Use WR to load data into the DAC input latch selected by A0 and A1.

WR

6

Data Inputs 7–0

D7–D0

7–14

Load DAC Input (active low). Drive the asynchronous LDAC input low to transfer the contents of all input

latches to their respective DAC latch.

LDAC

15

Reference Voltage Input

REF

4

Positive Supply Voltage. Bypass V

DD

to GND using a 0.1µF capacitor.

V

DD

3

PIN

DAC A Voltage Output

OUTA

2

DAC B Voltage Output

OUTB

1

FUNCTION

NAME

Detailed Description

Digital-to-Analog Section

The MAX5100 uses a matrix decoding architecture for

the DACs. The external reference voltage is divided

down by a resistor string placed in a matrix fashion.

Row and column decoders select the appropriate tab

from the resistor string to provide the needed analog

voltages. The resistor network converts the 8-bit digital

input into an equivalent analog output voltage in pro-

portion to the applied reference voltage input. The

resistor string presents a code-independent input

impedance to the reference and guarantees a monoton-

ic output.

The device can be used in multiplying applications.

The voltages are buffered by rail-to-rail op amps con-

nected in a follower configuration to provide a rail-to-rail

output. The functional block diagram for the MAX5100

is shown in Figure 2.

Low-Power Shutdown Mode

The MAX5100 features a shutdown mode that reduces

current consumption to 1nA. A high voltage on the

shutdown pin shuts down the DACs and the output

amplifiers. In shutdown mode, the output amplifiers

enter a high-impedance state. When bringing the

device out of shutdown, allow 13µs for the output to

stabilize.

Output Buffer Amplifiers

The DAC outputs are internally buffered by precision

amplifiers with a typical slew rate of 0.6V/µs. The typical

settling time to ±1/2LSB at the output is 6µs when

loaded with 10k

Ω in parallel with 100pF.

Reference Input

The MAX5100 provides a code-independent input

impedance on the REF input. The input impedance is

typically 460k

Ω in parallel with 15pF, and the reference

input voltage range is 0 to V

DD

. The reference input

accepts positive DC signals as well as AC signals with

peak values between 0 and V

DD

. The voltage at REF

sets the full-scale output voltage for the DAC. The out-

put voltage (V

OUT

) for any DAC is represented by a

digitally programmable voltage source as follows:

V

OUT

= (N

B

· V

REF

) / 256

where N

B

is the numeric value of the DAC binary input

code.

Digital Inputs and Interface Logic

In the MAX5100, address lines A0 and A1 select the

DAC that receives data from D0–D7, as shown in Table 1.

DAC C Voltage Output

OUTC

20

DAC Address Select Bit (LSB)

A0

17

Ground

GND

18

DAC D Voltage Output

OUTD

19