Typical operating characteristics – Rainbow Electronics MAX5100 User Manual

Page 4

MAX5100

+2.7V to +5.5V, Low-Power, Quad, Parallel

8-Bit DAC with Rail-to-Rail Voltage Outputs

4

_______________________________________________________________________________________

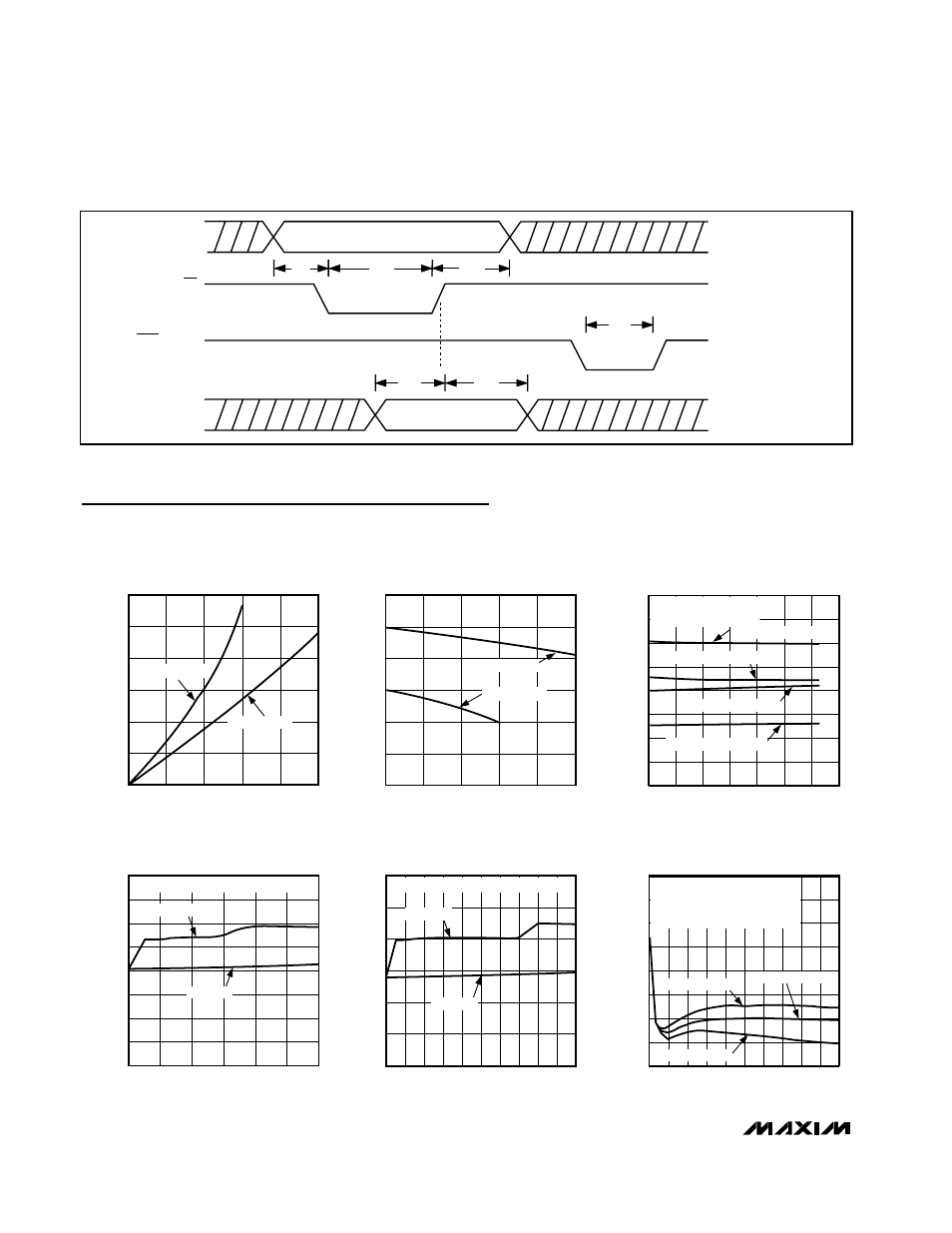

Typical Operating Characteristics

(V

DD

= V

REF

= +3V, R

L

= 10k

Ω, C

L

= 100pF, code = FF hex, T

A

= +25°C, unless otherwise noted.)

0

0.4

0.2

0.8

0.6

1.0

1.2

0

4

2

6

8

10

DAC ZERO-CODE OUTPUT VOLTAGE

vs. SINK CURRENT

MAX5100 toc01

SINK CURRENT (mA)

V

OUT

(V)

V

DD

= V

REF

= 3V

V

DD

= V

REF

= 5V

0

2

1

4

3

5

6

0

4

2

6

8

10

DAC FULL-SCALE OUTPUT VOLTAGE

vs. SOURCE CURRENT

MAX5100 toc02

SOURCE CURRENT (mA)

V

OUT

(V)

V

DD

= V

REF

= 3V

V

DD

= V

REF

= 5V

180

220

200

260

240

320

300

280

340

-40

0

-20

20

40

60

80

100

SUPPLY CURRENT vs. TEMPERATURE

MAX5100 toc03

TEMPERATURE (

°C)

SUPPLY CURRENT (

µ

A)

1 DAC AT CODE 00 OR F0,

3 DACS AT 00 (R

L

=

∞)

V

DD

= 5V; CODE = F0 HEX

V

DD

= 5V; CODE = 00 HEX

V

DD

= 3V; CODE = F0 HEX

V

DD

= 3V; CODE = 00 HEX

140

180

160

220

200

280

260

240

300

0

1.0

0.5

1.5

2.0

2.5

3.0

SUPPLY CURRENT vs. REFERENCE VOLTAGE

(V

DD

= 3V)

MAX5100 toc04

REFERENCE VOLTAGE (V)

SUPPLY CURRENT (

µ

A)

1 DAC AT CODE 00 OR F0, 3 DACS AT 00 (R

L

=

∞)

CODE = F0

CODE = 00

200

240

220

300

280

260

320

0

1.0

0.5

1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0

SUPPLY CURRENT vs. REFERENCE VOLTAGE

(V

DD

= 5V)

MAX5100 toc05

REFERENCE VOLTAGE (V)

SUPPLY CURRENT (

µ

A)

1 DAC AT CODE 00 OR F0, 3 DACS AT 00 (R

L

=

∞)

CODE = F0

CODE = 00

-80

-60

-70

-50

-20

-10

-30

-40

0

0

0.5

1.0

1.5

2.0

2.5

TOTAL HARMONIC DISTORTION PLUS NOISE

AT DAC OUTPUT vs. REFERENCE AMPLITUDE

MAX5100 toc06

REFERENCE AMPLITUDE (V

p-p

)

THD + NOISE (dB)

V

DD

= +3V

DAC CODE = FF HEX

V

REF

= SINE WAVE CENTERED AT 1.5V

80kHz FILTER

20kHz REF SIGNAL

10kHz REF SIGNAL

1kHz REF SIGNAL

ADDRESS VALID

DATA VALID

t

AS

t

WR

t

DS-

t

DH-

t

AH-

ADDRESS

DATA

WR

t

LD

LDAC (NOTE 8)

Figure 1. Timing Diagram