Electrical characteristics – Rainbow Electronics ADC0817 User Manual

Page 4

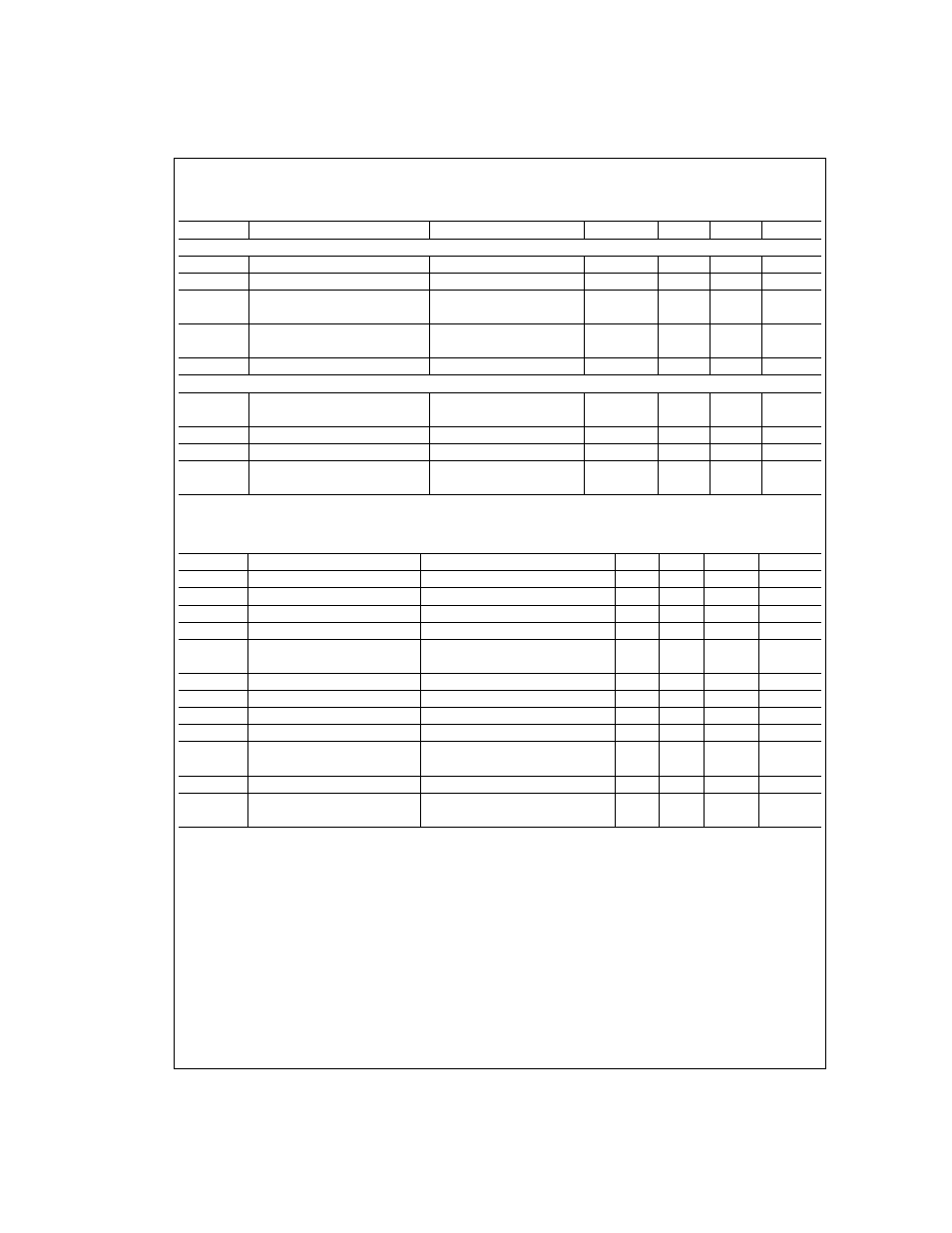

Electrical Characteristics

(Continued)

Digital Levels and DC Specifications: ADC0816CCJ, ADC0816CCN, ADC0817CCN — 4.75V

≤

V

CC

≤

5.25V, −40˚C

≤

T

A

≤

+85˚C

unless otherwise noted.

Symbol

Parameter

Conditions

Min

Typ

Max

Units

CONTROL INPUTS

V

IN(1)

Logical “1” Input Voltage

V

CC

−1.5

V

V

IN(0)

Logical “0” Input Voltage

1.5

V

I

IN(1)

Logical “1” Input Current

V

IN

=15V

1.0

µA

(The Control Inputs)

I

IN(0)

Logical “0” Input Current

V

IN

=0

−1.0

µA

(The Control Inputs)

I

CC

Supply Current

f

CLK

=640 kHz

0.3

3.0

mA

DATA OUTPUTS AND EOC (INTERRUPT)

V

OUT(1)

Logical “1” Output Voltage

I

O

−360 µA, T

A

=85˚C

V

CC

−0.4

V

I

O

=−300 µA, T

A

=125˚C

V

OUT(0)

Logical “0” Output Voltage

I

O

=1.6 mA

0.45

V

V

OUT(0)

Logical “0” Output Voltage EOC

I

O

=1.2 mA

0.45

V

I

OUT

TRI-STATE Output Current

V

O

=V

CC

3.0

µA

V

O

=0

−3.0

µA

Electrical Characteristics

Timing Specifications: V

CC

=V

REF(+)

=5V, V

REF(−)

=GND, t

r

=t

f

=20 ns and T

A

=25˚C unless otherwise noted.

Symbol

Parameter

Conditions

Min

Typ

Max

Units

t

WS

Minimum Start Pulse Width

(

Figure 5

) (Note 7)

100

200

ns

t

WALE

Minimum ALE Pulse Width

(

Figure 5

)

100

200

ns

t

s

Minimum Address Set-Up Time

(

Figure 5

)

25

50

ns

T

H

Minimum Address Hold Time

(

Figure 5

)

25

50

ns

t

D

Analog MUX Delay Time

R

S

=O

Ω

(

Figure 5

)

1

2.5

µS

from ALE

t

H1

, t

H0

OE Control to Q Logic State

C

L

=50 pF, R

L

=10k (

Figure 8

)

125

250

ns

t

1H,

t

0H

OE Control to Hi-Z

C

L

=10 pF, R

L

=10k (

Figure 8

)

125

250

ns

t

C

Conversion Time

f

c

=640 kHz, (

Figure 5

) (Note 8)

90

100

116

µs

f

c

Clock Frequency

10

640

1280

kHz

t

EOC

EOC Delay Time

(

Figure 5

)

0

8+2µs

Clock

Periods

C

IN

Input Capacitance

At Control Inputs

10

15

pF

C

OUT

TRI-STATE Output

At TRI-STATE Outputs (Note 8)

10

15

pF

Capacitance

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not apply when operating

the device beyond its specified operating conditions.

Note 2: All voltages are measured with respect to GND, unless otherwise specified.

Note 3: A zener diode exists, internally, from V

CC

to GND and has a typical breakdown voltage of 7 V

DC

.

Note 4: Two on-chip diodes are tied to each analog input which will forward conduct for analog input voltages one diode drop below ground or one diode drop greater

than the V

CC

supply. The spec allows 100 mV forward bias of either diode. This means that as long as the analog V

IN

does not exceed the supply voltage by more

than 100 mV, the output code will be correct. To achieve an absolute 0 V

DC

to 5 V

DC

input voltage range will therefore require a minimum supply voltage of 4.900

V

DC

over temperature variations, initial tolerance and loading.

Note 5: Total unadjusted error includes offset, full-scale, and linearity errors. See

Figure 3. None of these A/Ds requires a zero or full-scale adjust. However, if an

all zero code is desired for an analog input other than 0.0V, or if a narrow full-scale span exists (for example: 0.5V to 4.5V full-scale) the reference voltages can be

adjusted to achieve this. See

Figure 13.

Note 6: Comparator input current is a bias current into or out of the chopper stabilized comparator. The bias current varies directly with clock frequency and has little

temperature dependence (

Figure 6). See paragraph 4.0.

Note 7: If start pulse is asynchronous with converter clock or if f

c

>

640 kHz, the minimum start pulse width is 8 clock periods plus 2 µs. For synchronous operation

at f

c

≤

640 kHz take start high within 100 ns of clock going low.

Note 8: The outputs of the data register are updated one clock cycle before the rising edge of EOC.

Note 9: Human body model, 100 pF discharged through a 1.5 k

Ω

resistor.

www.national.com

4