Pin description – Rainbow Electronics MAX5093 User Manual

Page 9

MAX5092/MAX5093

4V to 72V Input LDOs with Boost Preregulator

_______________________________________________________________________________________

9

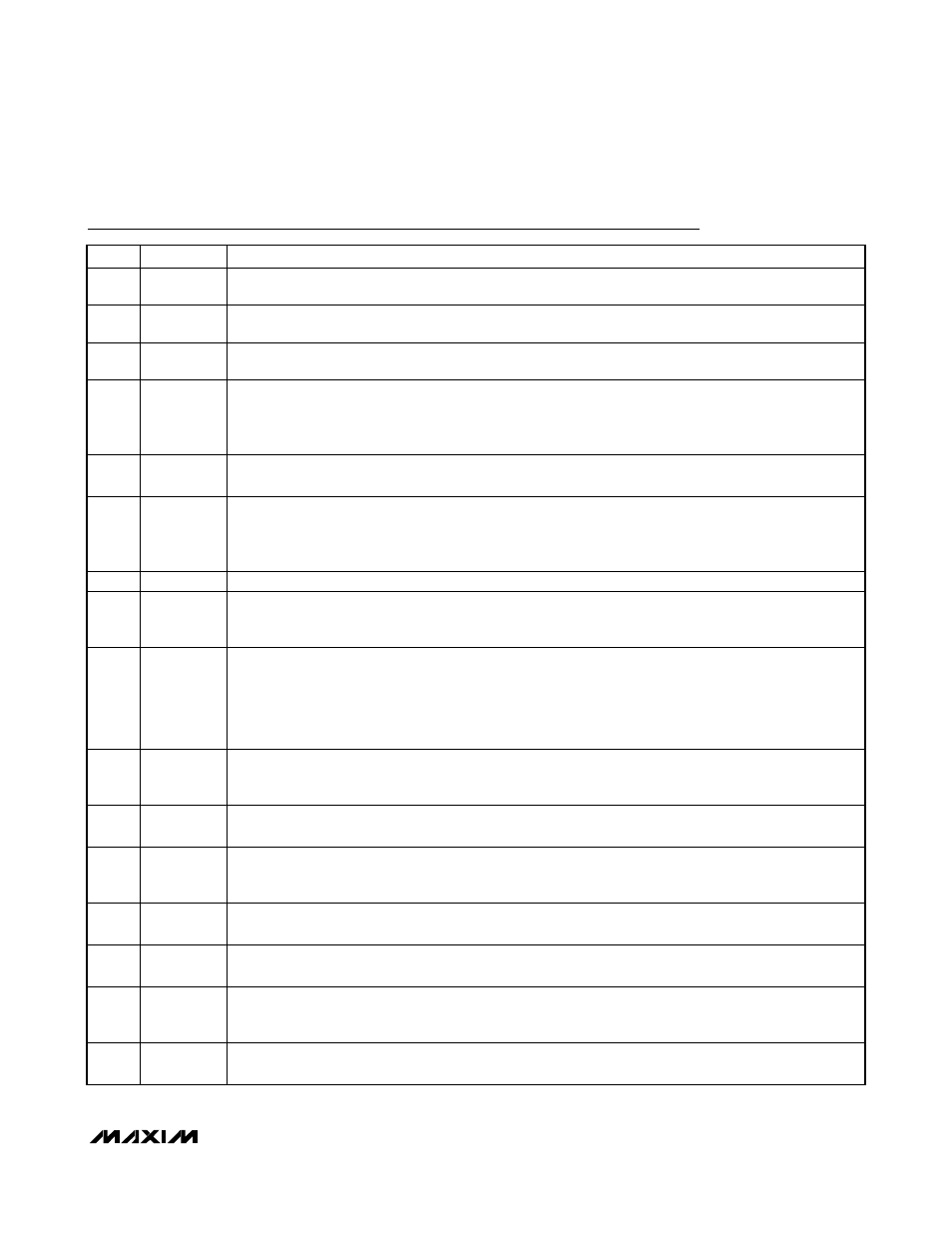

Pin Description

PIN

NAME

FUNCTION

1

IN

Input Supply Voltage. Bypass IN to the power ground plane with a 47µF (low-ESR) aluminum electrolytic

capacitor in parallel with a 1µF ceramic capacitor placed as close to the IC as possible.

2

EN

Enable Input. Drive EN high to turn on the IC. Drive EN low to disable the IC. Connect EN directly to IN for

always-on operation.

3

SGND

Signal Ground. Connect SGND to the signal ground plane and the exposed paddle. Connect the power

ground and signal ground plane together at the negative terminal of the input capacitor(s).

4

HOLD

Output Hold. When HOLD is forced low, the regulator stores the on-state of the output, allowing the

regulator to remain enabled even if EN is pulled low. To shut down the regulator, release HOLD after EN is

pulled low. If HOLD is unused, either connect HOLD to OUT or leave unconnected. HOLD is internally

connected to OUT through a 4µA pullup current.

5

PGND_LDO

LDO Power Ground. Connect PGND_LDO to the power ground plane. Connect the PGND_LDO ground and

signal ground plane together.

6

SET

Feedback Input for the LDO. Connect SET directly to SGND to set the output voltage of the LDO to the

preset voltage of 3.3V (MAX5092A/MAX5093A) or 5V (MAX5092B/MAX5093B). Connect SET to the center

tap of a resistor-divider connected between the LDO output and SGND to set the output voltage. V

SET

regulates to 1.24V when using an adjustable output.

7

OUT_SENSE

LDO Regulator Output Sense. Connect OUT_SENSE to OUT at the output capacitor near the load.

8

OUT

LDO Regulator Output. Bypass OUT to the power ground plane with a 10µF ceramic capacitor. V

OUT

regulates to a preset voltage of 3.3V (MAX5092A/MAX5093A) or 5V (MAX5092B/MAX5093B), or is

adjustable from 1.5V to 9V (MAX5902_) or 1.5V to 10V (MAX5093_).

9

BSOUT

Boost Regulator Output Voltage. Bypass BSOUT to the PGND_BST ground plane with a 22µF (low-ESR)

aluminum electrolytic capacitor in parallel with a 1µF ceramic capacitor placed as close to the IC as

possible. Connect BSFB directly to SGND to regulate the BOOST output to a fixed voltage of 7V for V

IN

≤

7V. V

BSOUT

follows V

IN

for V

IN

> 7V. V

BSOUT

is programmable up to 11V (MAX5092_) or 12V (MAX5093_)

by connecting BSFB to the center tap of an external resistor-divider connected between the BOOST output

and PGND_BST.

10, 11

LX

Inductor Connection to the Drain of the Internal Power MOSFET. Connect LX to the switched side of the

inductor. Connect pins 10 and 11 together as close to the device as possible. For the MAX5093, also

connect LX to the anode of the external Schottky diode.

12

PGND_BST

Boost Regulator Power Ground. Connect PGND_BST to the power ground plane. Connect the PGND_BST

ground plane and the signal ground plane together at the negative terminal of the input capacitor(s).

13

BSFB

Feedback Input for the Boost Regulator. Connect BSFB directly to SGND to set the boost regulator output

voltage to 7V. Connect BSFB to the center tap of an external resistor-divider connected between BSOUT

and SGND to set the output voltage. V

BSFB

regulates to 1.24V when using an adjustable output.

14

VL

Internal Regulator Output for IC Supply. Bypass VL to SGND with a 1µF/6.3V ceramic capacitor placed as

close to the IC as possible. V

VL

regulates to 5.5V with V

BSOUT

≥ 5.5V.

15

CT

RESET Timeout Programming Input. Connect a capacitor from CT to SGND to set the RESET timeout

period. See the CT Capacitor Selection section.

16

RESET

RESET Output. RESET is an open-drain output that goes high impedance when V

OUT

exceeds 92% of the

output voltage threshold after a programmed time delay. RESET pulls low immediately once V

OUT

drops

below 90% of the regulated LDO output voltage.

—

EP

Exposed Paddle. Connect to the signal ground plane (SGND). Connect to a large-signal ground plane for

increased thermal performance.