Rainbow Electronics MAX5093 User Manual

Page 13

MAX5092/MAX5093

4V to 72V Input LDOs with Boost Preregulator

______________________________________________________________________________________

13

Internal Regulator (VL)

An internal regulator (VL) is used to supply all internal

low-voltage blocks. Bypass VL to SGND with a 1µF

ceramic capacitor placed as close to the IC as possi-

ble. V

VL

regulates to 5.5V when V

BSOUT

is above 5.5V.

V

VL

tracks the voltage at BSOUT when V

BSOUT

is

below 5.5V.

Power-On-Reset Output (

RESET)

The MAX5092_/MAX5093_ contain an open-drain output

(RESET) that indicates when the LDO output (V

OUT

) is

out of regulation. If the output of the LDO falls below 90%

of the nominal output voltage, RESET pulls low after a

short delay. Once the output rises above 92% of the

nominal output voltage, RESET goes high impedance

after the programmed reset timeout period. Connect a

100kΩ pullup resistor from OUT to RESET. See the

CT

Capacitor Selection

section for details on setting the

RESET timeout period.

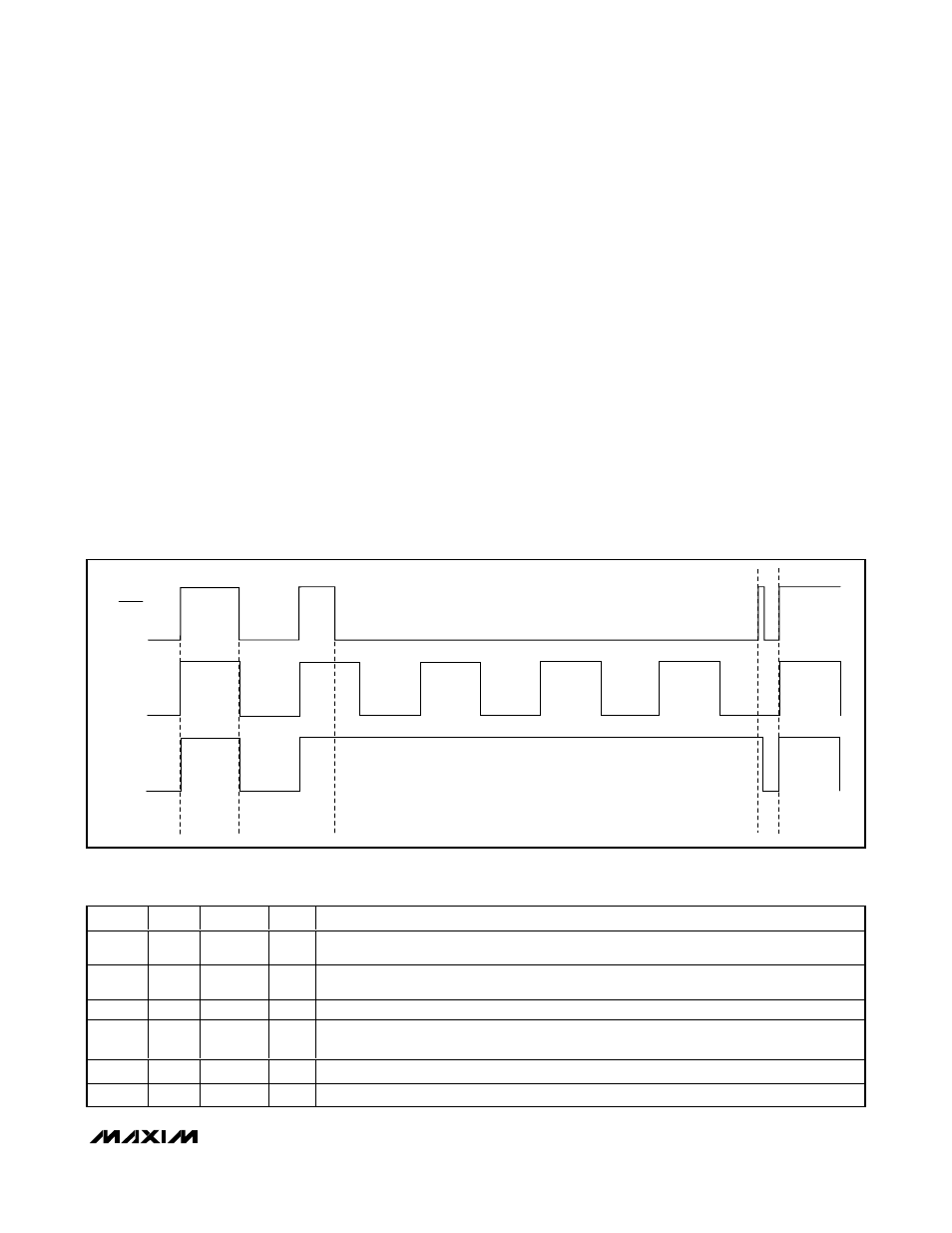

Enable and Hold Inputs

The MAX5092_/MAX5093_ utilize two logic inputs, EN

(active-high) and HOLD (active low), to implement a

self-holding circuit with no additional components. For

example, an automotive ignition switch drives EN high

and the regulator turns on. If HOLD is then driven low,

the regulator remains on even if EN goes low. As long

as HOLD is forced low and remains low after initial reg-

ulator power-up, the regulator remains on. From this

state, release HOLD (an internal current source con-

nects HOLD to OUT), or connect HOLD to OUT to turn

the regulator off. Drive EN low and HOLD high to place

the IC into shutdown mode. Shutdown mode reduces

supply current to 5µA. Figure 3 shows the timing dia-

gram for the enable and hold functions. Table 1 shows

the state of the regulator output with respect to the volt-

age level at EN and HOLD with reference to Figure 3.

Connect HOLD to OUT or leave unconnected to dis-

able the hold feature and use EN as a standard on/off

control input.

3

1

HOLD

EN

OUT

ORDER

2

4

5

6

Figure 3. Enable and Hold Timing Diagram

ORDER

EN

HOLD

OUT

COMMENTS

1

Low

X

Off

Initial State. EN has a 500nA pulldown to GND. HOLD has an internal current source to OUT.

HOLD follows OUT.

2

High

Released

On

Regulator output is active when EN is pulled high. HOLD is in release state, and it follows

OUT.

3

Low

Released

Off

HOLD is in release state. OUT follows EN.

4

High

Low

On

HOLD is pulled low externally after OUT turns on. The regulator output is forced on

regardless of the state of EN. A self-holding state.

5

Low

Released

Off

HOLD is released after EN is pulled low. Output turns off.

5

High

X

On

Regulator enabled. Normal turn-on behavior. Regulator follows EN and HOLD follows OUT.

Table 1. Truth Table for Enable and Hold Timing Diagram