Programming – Rainbow Electronics MAX31723 User Manual

Page 10

MAX31722/MAX31723

Digital Thermometers and Thermostats

with SPI/3-Wire Interface

10

In either mode, once TOUT has been deactivated, it is

only reactivated when the measured temperature falls

below the T

LOW

value. Thus, this interrupt/clear pro-

cess is cyclical between T

HIGH

and T

LOW

events (i.e,

T

HIGH

, clear, T

LOW

, clear, T

HIGH

, clear, T

LOW

, clear,

etc.). Figure 6 illustrates the thermostat interrupt mode

operation.

Programming

The area of interest in programming the devices is the

configuration/status register. All programming is done

through the SPI or 3-wire communication interface by

selecting the appropriate address of the desired register

location. Table 2 illustrates the addresses for the device

registers.

Configuration/Status Register Programming

The configuration/status register is accessed in the

devices with the 00h address for reads and the 80h

address for writes. Data is read from or written to the

configuration/status register MSB first for SPI communi-

cation and LSB first for 3-wire communication. Table 3

illustrates the format of the register, describes the effect

each bit has on device functionality, and provides the

bit’s factory state.

Table 4 defines the resolution of the digital thermometer,

based on the settings of the R1 and R0 bits. There is a

direct trade-off between resolution and conversion time,

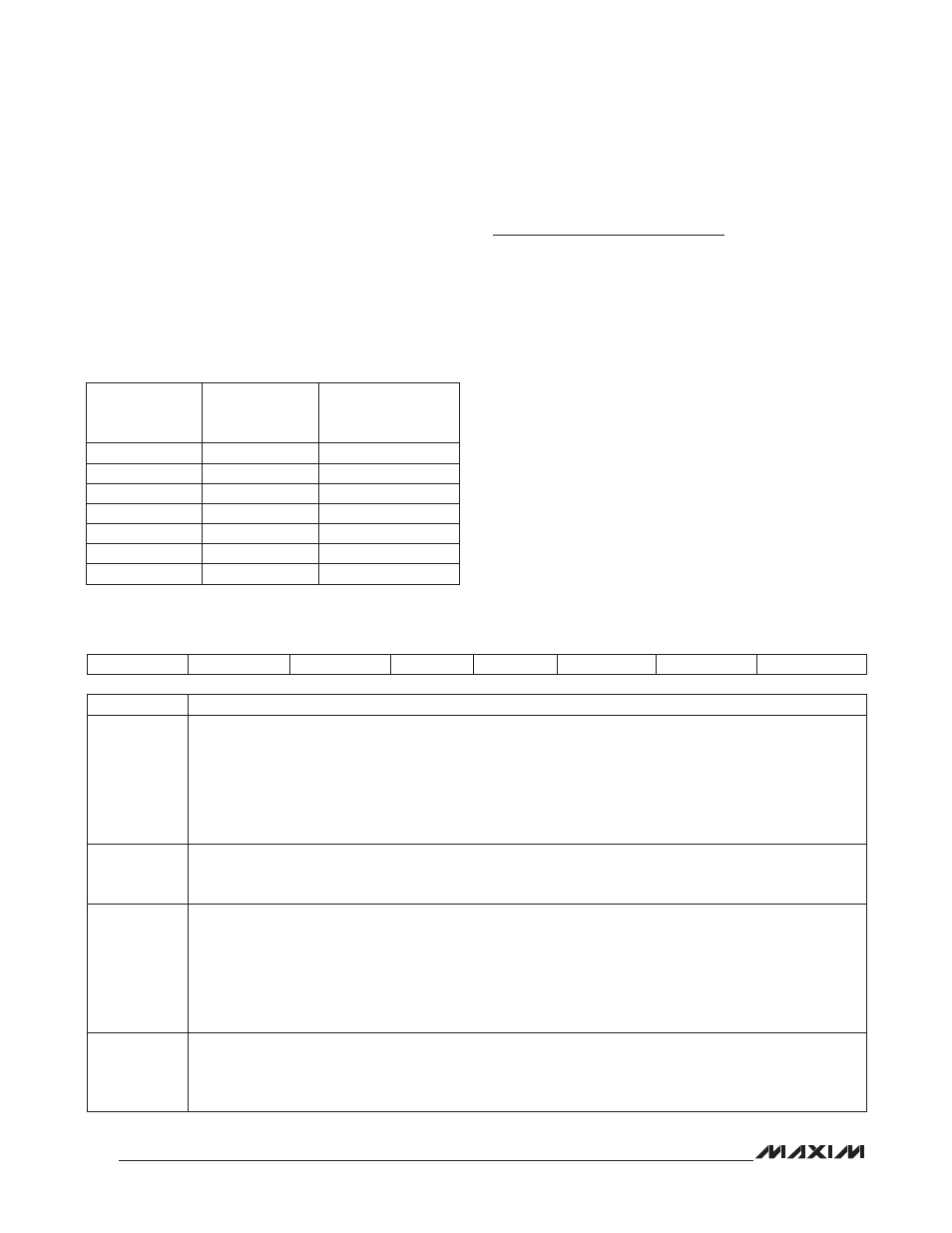

Table 2. Register Address Structure

Table 3. Configuration/Status Register Bit Descriptions

READ

ADDRESS

(HEX)

WRITE

ADDRESS

(HEX)

ACTIVE REGISTER

00

80

Configuration/Status

01

No access

Temperature LSB

02

No access

Temperature MSB

03

83

T

HIGH

LSB

04

84

T

HIGH

MSB

05

85

T

LOW

LSB

06

86

T

LOW

MSB

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

0

MEMW

NVB

1SHOT

TM

R1

R0

SD

BIT 7

This bit is always a value of 0.

BIT 6

MEMW: Memory write bit. Power-up state = 0. The user has read/write access to the MEMW bit, which is

stored in the voltage memory.

0 = A write of the configuration/status register is stored in RAM memory.

1 = A write of the configuration/status register is stored in EEPROM.

Note: The status of this bit is ignored if a EEPROM write occurs to the other nonvolatile registers, T

HIGH

and

T

LOW

. The nonvolatile bits of the configuration/status register are written if a EEPROM write cycle occurs to the

T

HIGH

and T

LOW

registers.

BIT 5

NVB: Nonvolatile memory busy flag. Power-up state = 0 and is stored in volatile memory.

0 = Indicates that the nonvolatile memory is not busy.

1 = Indicates there is a write to a EEPROM memory cell in progress.

BIT 4

1SHOT: One-shot temperature conversion bit. Power-up state = 0 and is stored in volatile memory.

0 = Disables 1SHOT mode.

1 = If the SD bit is 1 (continuous temperature conversions are not taking place), a 1 written to the 1SHOT bit

causes the devices to perform one temperature conversion and store the results in the temperature register

at addresses 01h (LSB) and 02h (MSB). The bit clears itself to 0 upon completion of the temperature conver-

sion. The user has read/write access to the 1SHOT bit, although writes to this bit are ignored if the SD bit is a 0

(continuous conversion mode).

BIT 3

TM: Thermostat operating mode. Factory power-up state = 0. The user has read/write access to the TM bit,

which is stored in nonvolatile memory.

0 = The thermostat output is in comparator mode.

1 = The thermostat output is in interrupt mode.