Electrical characteristics (max5259) (continued), Timing characteristics (max5258) – Rainbow Electronics MAX5259 User Manual

Page 5

MAX5258/MAX5259

+3V/+5V, Low-Power, 8-Bit Octal DAC

with Rail-to-Rail Output Buffers

_______________________________________________________________________________________

5

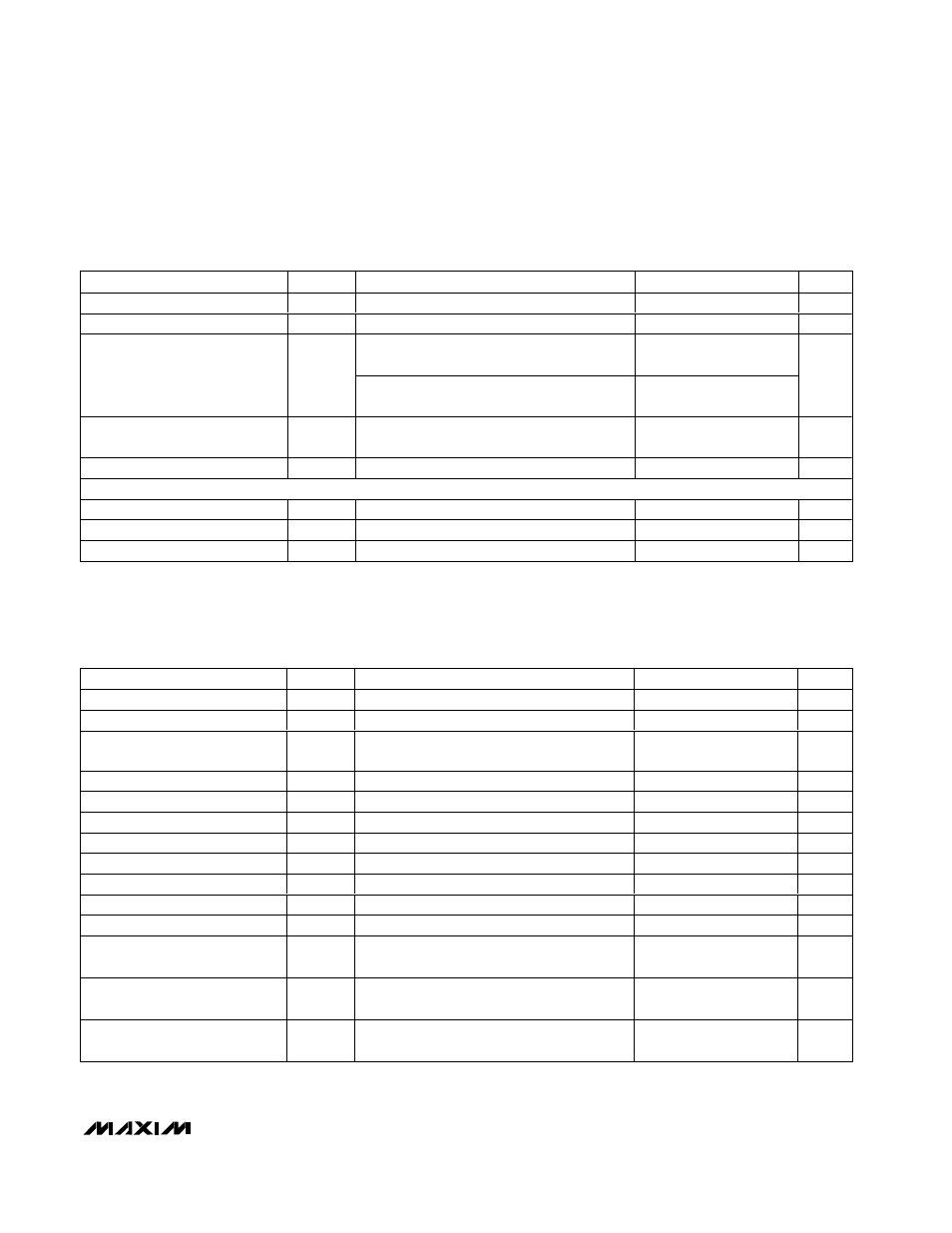

ELECTRICAL CHARACTERISTICS (MAX5259) (continued)

(V

DD

= +2.7V to +3.3V, V

REF

= +2.5V, GND = 0, R

L

= 10k

Ω, C

L

= 100pF, T

A

= T

MIN

to T

MAX

, unless otherwise noted. Typical values

are at V

DD

= +3V, and T

A

= +25°C.)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

Digital Feedthrough

Code = 00 hex

0.1

nV-s

Digital-to-Analog Glitch Impulse

Code = 80 to code = 7F hex

20

nV-S

V

REF

= 2.5V

p-p

at 1kHz centered at 1.5V

code = FF hex

65

Signal-to-Noise Plus Distortion

Ratio

SINAD

V

REF

= 2.5V

p-p

at 10kHz centered at 1.5V

code = FF hex

54

dB

Multiplying Bandwidth

V

REF

= 0.1V

p-p

centered at V

DD

/2, -3dB

bandwidth

700

kHz

Wideband Amplifier Noise

60

µV

POWER REQUIREMENTS

Power-Supply Voltage

V

DD

2.7

3.6

V

Supply Current

I

DD

1.3

2.6

mA

Shutdown Supply Current

I

SHDN

0.24

10

µA

TIMING CHARACTERISTICS (MAX5258)

(V

REF

= +4.096V, GND = 0, C

DOUT

= 100pF, T

A

= T

MIN

to T

MAX

, unless otherwise noted. Typical values are at V

DD

= +5V and

T

A

= +25°C.)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

V

DD

Rise-to-CS Fall-Setup Time

t

VDCS

5

µs

LDAC Pulse Width Low

t

LDAC

40

20

ns

CS Rise-to-LDAC Fall-Setup Time

(Note 4)

t

CLL

40

ns

CS Pulse Width High

t

CSW

90

ns

SCLK Clock Frequency (Note 5)

f

CLK

10

MHz

SCLK Pulse Width High

t

CH

40

ns

SCLK Pulse Width Low

t

CL

40

ns

CS Fall-to-SCLK Rise-Setup Time

t

CSS

40

ns

SCLK Rise-to-CS Rise-Hold Time

t

CSH

0

ns

DIN to SCLK Rise-to-Setup Time

t

DS

40

ns

DIN to SCLK Rise-to-Hold Time

t

DH

0

ns

SCLK Rise-to-DOUT Valid

Propagation Delay (Note 6)

t

DO1

200

ns

SCLK Fall-to-DOUT Valid

Propagation Delay (Note 7)

t

DO2

210

ns

CS Rise-to-SCLK Rise-Setup

Time

t

CS1

40

ns