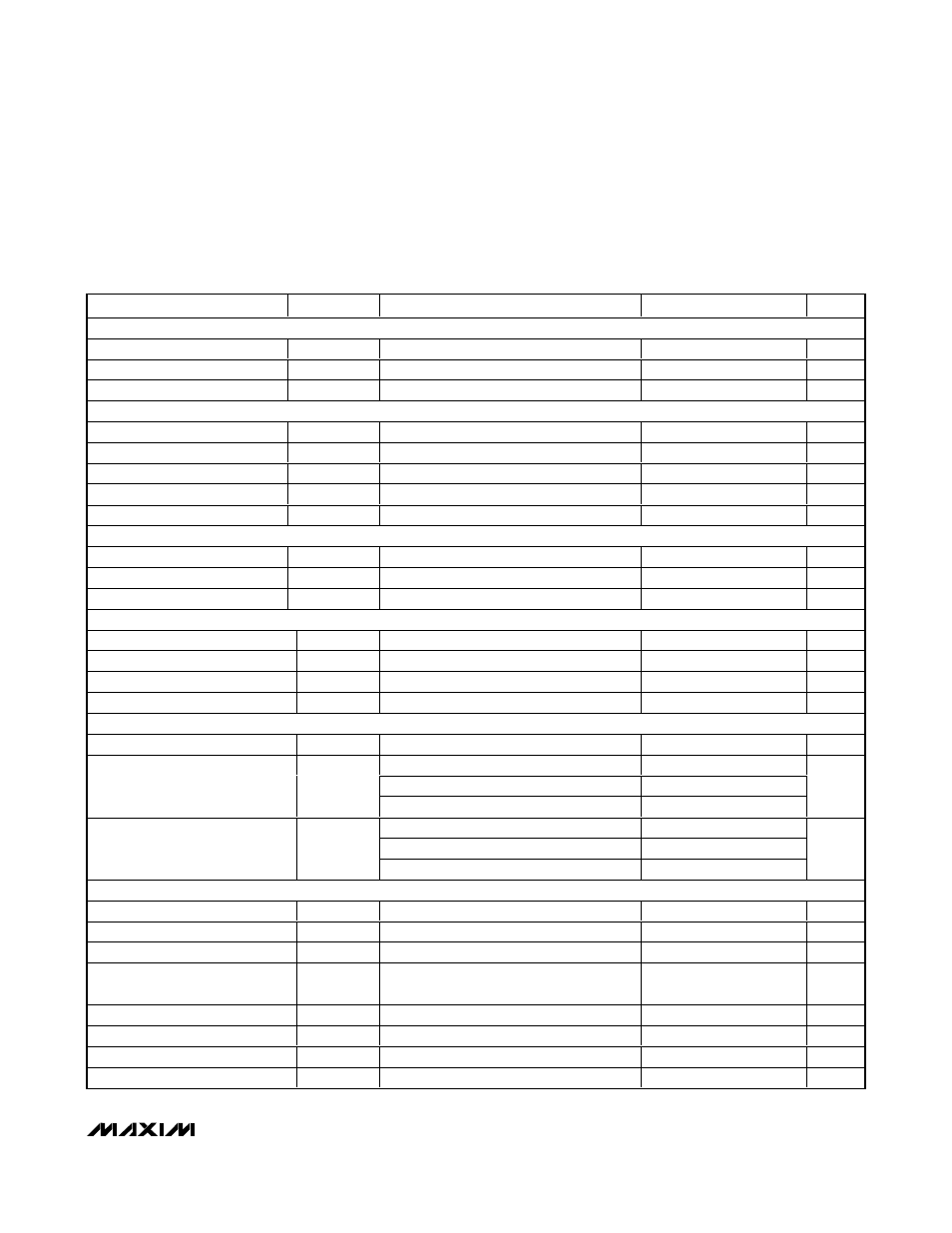

Electrical characteristics (continued) – Rainbow Electronics MAX5559 User Manual

Page 3

MAX5556–MAX5559

Low-Cost Stereo Audio DACs

_______________________________________________________________________________________

3

ELECTRICAL CHARACTERISTICS (continued)

(V

DD

= +4.75V to +5.5V, GND = 0V, R

OUT

_ = 10kΩ, C

OUT

_ = 10pF, 0dBFS sine-wave signal at 997Hz, f

LRCLK

(f

S

) = 48kHz, f

MCLK

=

12.288MHz, measurement bandwidth 10Hz to 20kHz, unless otherwise specified. T

A

= -40°C to +85°C, unless otherwise noted.

Outputs are unloaded, unless otherwise noted. Typical values at V

DD

= +5V, T

A

= +25°C.) (Note 1)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

DC CHARACTERISTICS

Interchannel Gain Mismatch

0.1

0.4

dB

Gain Error

-5

+5

%

Gain Drift

100

ppm/°C

ANALOG OUTPUTS

Full-Scale Output Voltage

V

OU T R

, V

OU T L

3.25

3.5

3.75

V

P-P

DC Quiescent Output Voltage

V

Q

Input code = 0

2.4

V

Minimum Load Resistance

R

L

3

k

Ω

Maximum Load Capacitance

C

L

100

pF

Power-Supply Rejection Ratio

PSRR

V

RIPPLE

= 100mV

P-P

, frequency = 1kHz

66

dB

POP AND CLICK SUPPRESSION

Mute Attenuation

100

dB

Power-Up Until Bias Established

Figure 14

360

ms

Valid Clock to Normal Operation

Soft-start ramp time, Figure 15 (Note 5)

20

ms

DIGITAL AUDIO INTERFACE (SCLK, SDATA, MCLK, LRCLK)

Input-Voltage High

V

IH

2.0

V

Input-Voltage Low

V

IL

0.8

V

Input Leakage Current

I

IN

-10

+10

µA

Input Capacitance

8

pF

TIMING CHARACTERISTICS

Input Sample Rate

f

S

2

50

kHz

MCLK/LRCLK = 512

10

MCLK/LRCLK = 384

20

MCLK Pulse-Width Low

t

MCLKL

MCLK/LRCLK = 256

20

ns

MCLK/LRCLK = 512

10

MCLK/LRCLK = 384

20

MCLK Pulse-Width High

t

MCLKH

MCLK/LRCLK = 256

20

ns

EXTERNAL SCLK MODE

LRCLK Duty Cycle

(Note 6)

25

75

%

SCLK Pulse-Width Low

t

SCLKL

20

ns

SCLK Pulse-Width High

t

SCLKH

20

ns

SCLK Period

t

SCLK

1 / (128

x f

S

)

ns

LRCLK Edge to SCLK Rising

t

SLRS

20

ns

LRCLK Edge to SCLK Rising

t

SLRH

20

ns

SDATA Valid to SCLK Rising

t

SDS

20

ns

SCLK Rising to SDATA Hold Time

t

SDH

20

ns