Rainbow Electronics MAX5133 User Manual

Page 4

MAX5132/MAX5133

+5V/+3V, 13-Bit, Serial, Force/Sense DACs

with 10ppm/°C Internal Reference

4

_______________________________________________________________________________________

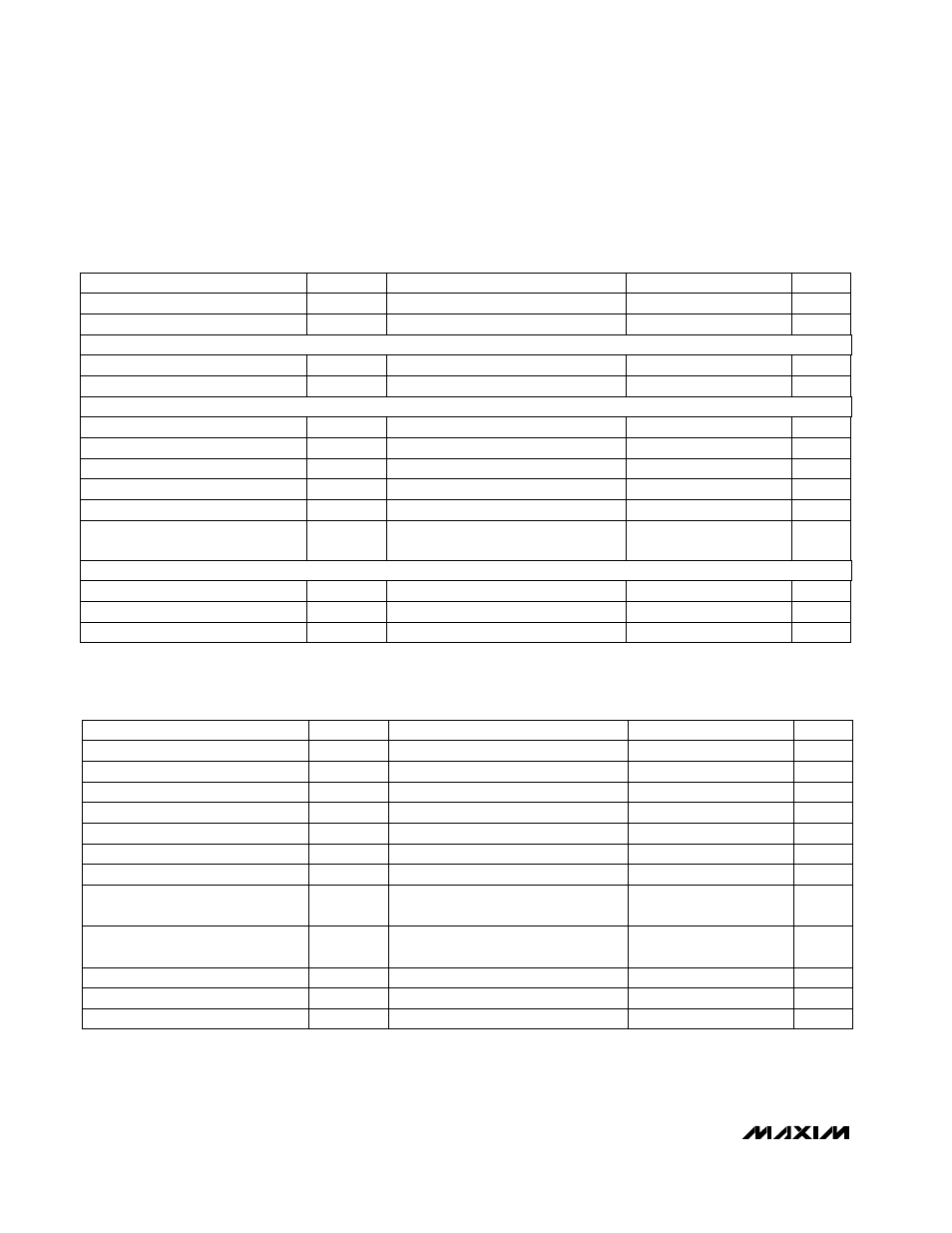

ELECTRICAL CHARACTERISTICS—MAX5133 (+3V) (continued)

(V

DD

= +3V ±10%, AGND = DGND, 33nF capacitor at REFADJ, internal reference, R

L

= 5k

Ω

, C

L

= 100pF, output amplifier

connected in unity-gain, T

A

= T

MIN

to T

MAX

, unless otherwise noted. Typical values are at T

A

= +25°C.)

To ±0.5LSB, V

STEP

= 1.25V

CS = V

DD

, f

SCLK

= 100kHz,

V

SCLK

= 3Vp-p

CONDITIONS

µA

3

20

I

SHDN

Power-Supply Current in Shutdown

µA

500

600

I

DD

Power-Supply Current (Note 5)

V

2.7

3.6

V

DD

Power-Supply Voltage (Note 5)

nV-s

5

Digital Feedthrough

ms

2

Time Required to Exit Shutdown

µA

-0.1

0

0.1

Current into FB

µs

20

Output Settling Time

V

0 to V

DD

Output Voltage Swing (Note 4)

UNITS

MIN

TYP

MAX

SYMBOL

PARAMETER

I

SINK

= 2mA

V

0.13

0.4

V

OL

Output Low Voltage

I

SOURCE

= 2mA

V

V

DD

- 0.5

V

OH

Output High Voltage

V

IN

= 0 or V

DD

µA

-1

0.001

1

I

IN

Input Leakage Current

pF

8

C

IN

Input Capacitance

V/µs

0.6

SR

Voltage Output Slew Rate

TIMING CHARACTERISTICS—MAX5132 (+5V)

(V

DD

= +5V ±10%, AGND = DGND, 33nF capacitor at REFADJ, internal reference, R

L

= 5k

Ω

, C

L

= 100pF, output amplifier connect-

ed in unity-gain, T

A

= T

MIN

to T

MAX

, unless otherwise noted. Typical values are at T

A

= +25°C.)

ns

40

t

CSS

CS Fall to SCLK Rise Setup Time

ns

40

t

CL

SCLK Pulse Width Low

CONDITIONS

ns

100

t

CP

SCLK Clock Period

ns

40

t

CH

SCLK Pulse Width High

ns

0

t

CSH

SCLK Rise to CS Rise Hold Time

ns

10

t

CS0

SCLK Rise to CS Fall Delay Time

ns

40

t

DS

SDI Setup Time

ns

0

t

DH

SDI Hold Time

UNITS

MIN

TYP

MAX

SYMBOL

PARAMETER

ns

100

t

CSW

CS Pulse Width High

ns

40

t

CS1

CS Rise to SCLK Rise Hold Time

C

LOAD

= 200pF

ns

80

t

DO1

SCLK Rise to DOUT Valid

Propagation Delay Time

C

LOAD

= 200pF

ns

80

t

DO2

SCLK Fall to DOUT Valid

Propagation Delay Time

DIGITAL OUTPUTS

POWER REQUIREMENTS

DYNAMIC PERFORMANCE