Chip information – Rainbow Electronics MAX5190 User Manual

Page 14

MAX5187/MAX5190

8-Bit, 40MHz, Current/Voltage-Output DACs

14

______________________________________________________________________________________

ic interference (EMI) can either couple into or be gener-

ated by the MAX5187/MAX5190. Therefore, grounding

and power-supply decoupling guidelines for high-

speed, high-frequency applications should be closely

followed.

First, a multilayer PC board with separate ground and

power-supply planes is recommended. High-speed

signals should be run on controlled impedance lines

directly above the ground plane. Since the MAX5187/

MAX5190 have separate analog and digital ground

buses (AGND and DGND, respectively), the PC board

should also have separate analog and digital ground

sections with only one point connecting the two. Digital

signals should run above the digital ground plane, and

analog signals should run above the analog ground

plane.

Both devices have two power-supply inputs: analog

V

DD

(AV

DD

) and digital V

DD

(DV

DD

). Each AV

DD

input

should be decoupled with parallel 10µF and 0.1µF

ceramic chip capacitors. These capacitors should be

as close to the pin as possible, and their opposite ends

should be as close as possible to the ground plane.

The DV

DD

pins should also have separate 10µF and

0.1µF capacitors adjacent to their respective pins. Try

to minimize the analog load capacitance for proper

operation. For best performance, bypass with low-ESR

0.1µF capacitors to AV

DD

.

The power-supply voltages should also be decoupled

with large tantalum or electrolytic capacitors at the

point they enter the PC board. Ferrite beads with addi-

tional decoupling capacitors forming a pi-network can

also improve performance.

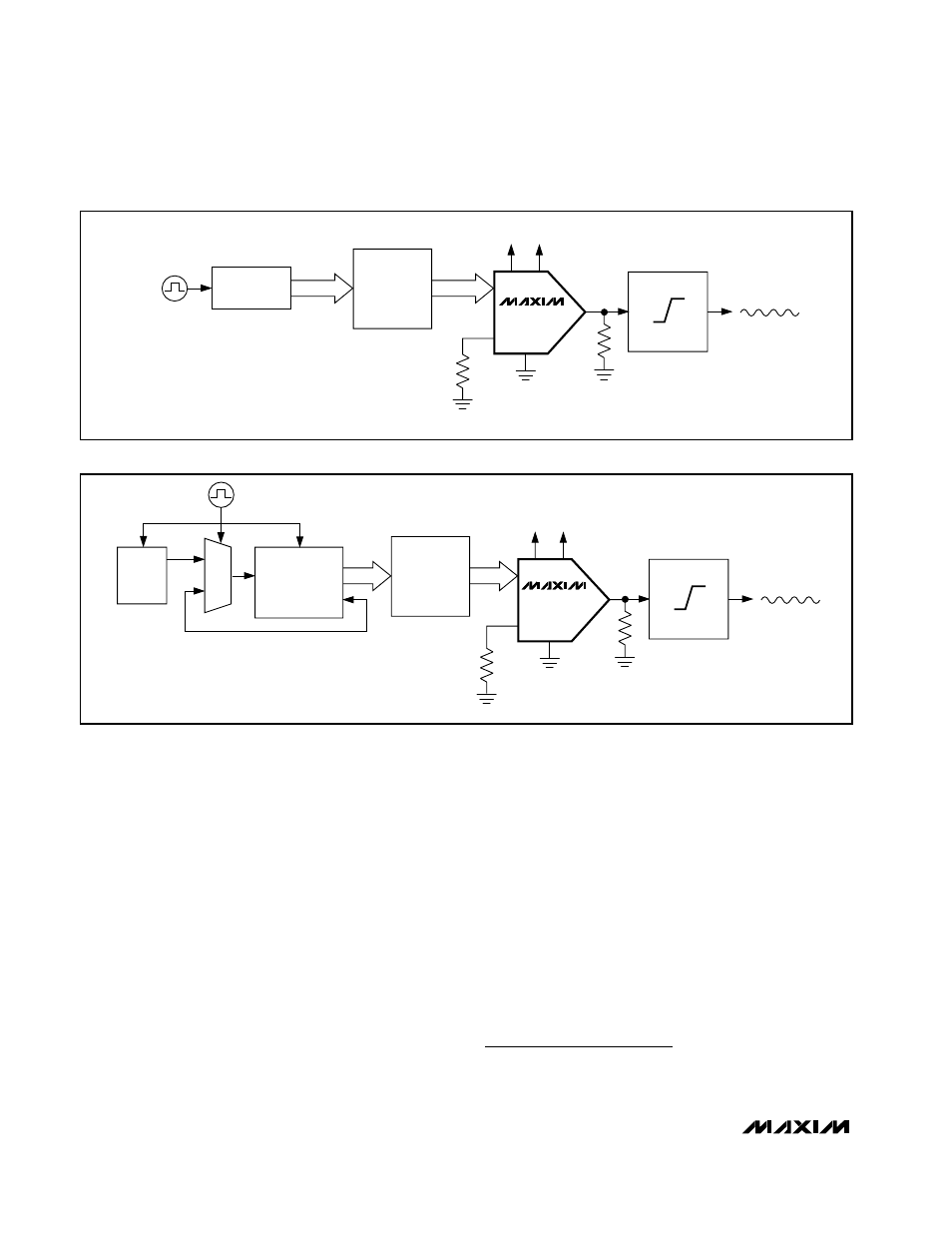

9.6k*

400

Ω*

WAVEFORM

MEMORY

(RAM)

CLOCK

GENERATOR

DV

DD

AV

DD

*MAX5187 ONLY

MAX5187

MAX5190

8

ADR

FILTERED

WAVEFORM

(ANALOG OUTPUT)

LOWPASS

RECONSTRUCTION

FILTER

VARIABLE

f

C

COUNTER

9.6k*

400

Ω*

WAVEFORM

MEMORY

(RAM)

DV

DD

AV

DD

*MAX5187 ONLY

MAX5187

MAX5190

8

DATA

REFR

ADR

A

D

D

E

R

FILTERED

WAVEFORM

(ANALOG OUTPUT)

LOWPASS

RECONSTRUCTION

FILTER

VARIABLE

f

C

PHASE

ACCUMULATOR

ACCUMULATOR

FEEDBACK LOOP

FOR DATA BITS

CLOCK

GENERATOR

PIR

PHASE

INCREMENT

REGISTER

Figure 8a. Traditional Arbitrary Waveform Generation (AWG)

Figure 8b. Direct Digital Synthesis AWG (DDS AWG)

Chip Information

TRANSISTOR COUNT: 9464

SUBSTRATE CONNECTED TO AGND