System reset, Evaluation version, Functional description – Xilinx LogiCore PLB PCI Full Bridge User Manual

Page 4: Logicore version 3.0 32-bit pci core requirements, Earl y access

PLB PCI Full Bridge (v1.00a)

4

w.xilinx.com

DS508 March 21, 2006

Product Specification

EARL

Y ACCESS

System Reset

When the bridge is reset, both RST_N and PLB_reset must be simultaneously held at reset for at least

twenty clock periods of the slowest clock.

Evaluation Version

The PLB PCI Bridge is delivered with a hardware evaluation license. When programmed into a Xilinx

device, the core will function in hardware for about 8 hours at the typical frequency of operation. To use

the PLB PCI Bridge without this timeout limitation, a full license must be purchased.

Functional Description

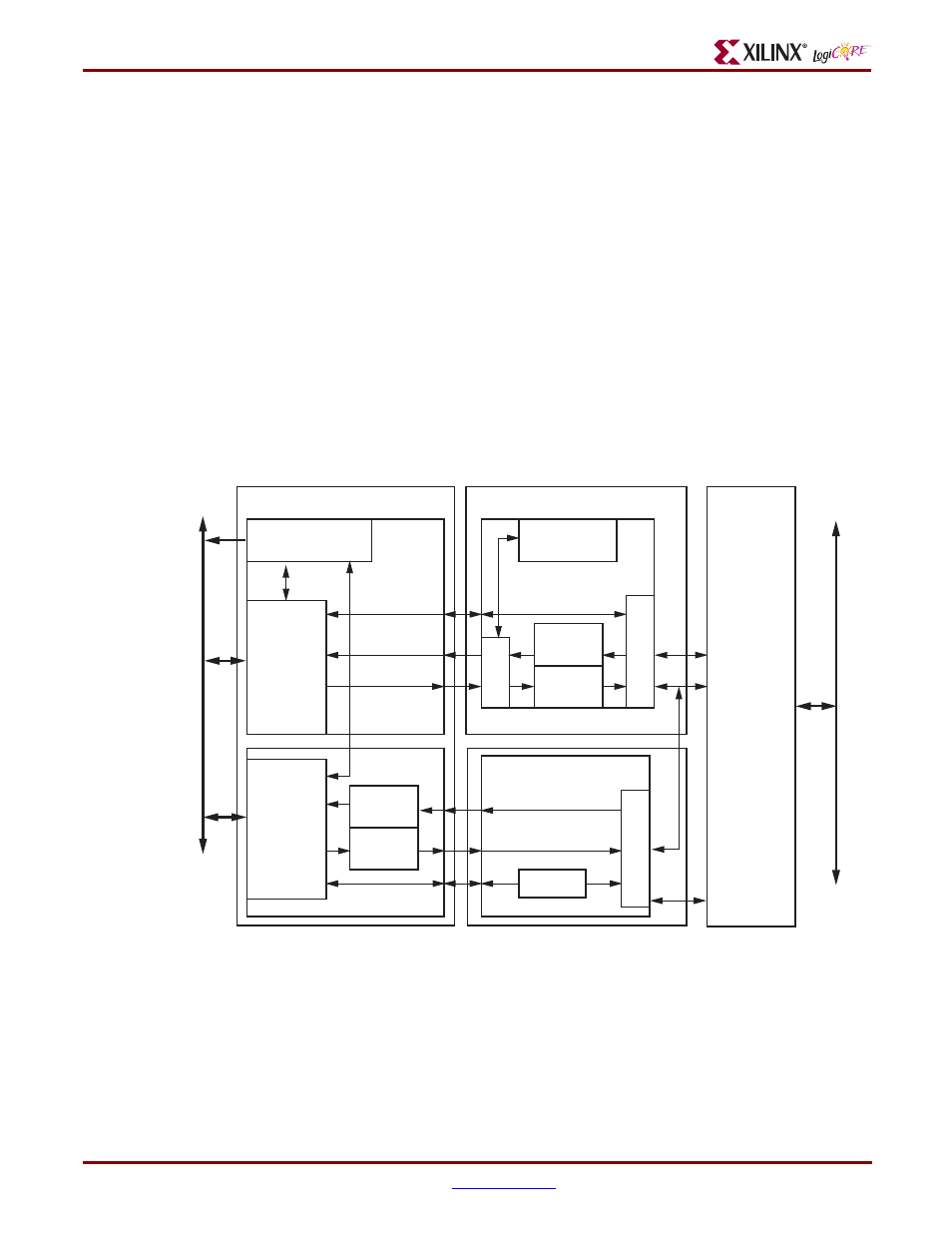

The PLB PCI Bridge design is shown in

and described in the following sections. As shown,

PLB IPIF PCI Bridge is comprised of three main modules:

• The PLB IPIF (Processor Local Bus Intellectual Property InterFace). It interfaces to the PLB bus.

• The IPIF v3.0 Bridge. It interfaces between the PLB IPIF and the v3.0 core.

• The LogiCORE PCI32 Interface v3.0 core. It interfaces to the PCI bus.

Figure 1: PLB PCI Full Bridge Block Diagram

Figure Top x-ref 1

PLB B

us

PCI B

us

ds508_01_112205

Bridge

Registers

IPIF2PCI

FIFO

PCI2IPIF

FIFO

S

la

ve

S

M

Initi

a

tor

Master SM

T

a

rget

Interrupt

Module

Slave

Attachment

Master

Attachment

IPIF2PCI

FIFO

PCI2IPIF

FIFO

PLB IPIF

IPIF/V3 Bridge

Xilinx

v3.0 PCI Core

LogiCore Version 3.0 32-bit PCI Core Requirements

The PLB PCI bridge uses the 32-bit Xilinx LogiCore Version 3 IP core. Before the bridge can perform

transactions on the PCI bus, the v3.0 core must be configured via configuration transactions from either

the PCI-side or if configuration functionality is included in the bridge configuration, from the PLB-side.

Both a design guide and an implementation guide are available for the Xilinx LogiCore v3.0 PCI IP