Terminal functions – Texas Instruments TPA3003D2 User Manual

Page 4

TPA3003D2

SLOS406A − FEBRUARY 2003 − REVISED MARCH 2003

4

www.ti.com

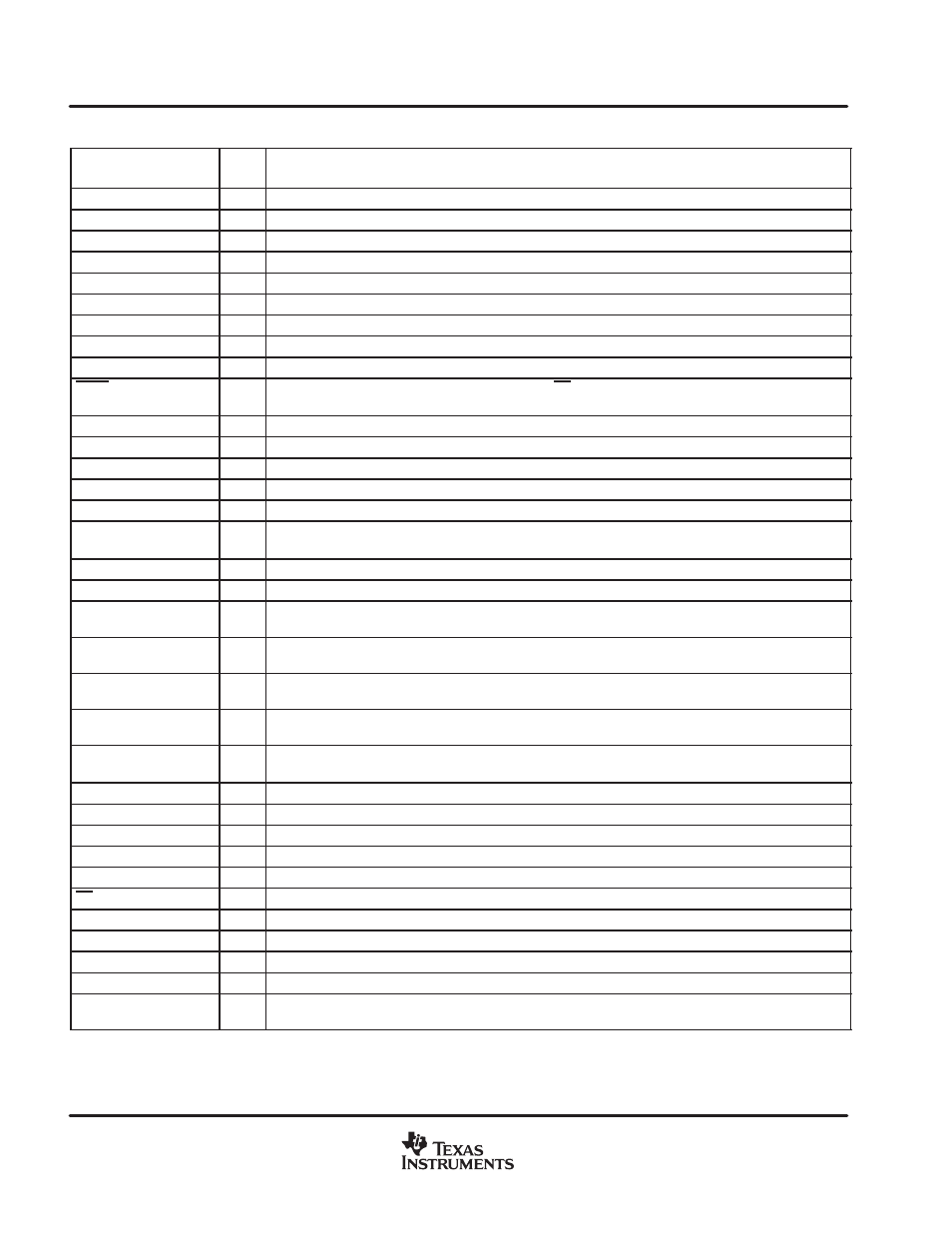

Terminal Functions

TERMINAL

I/O

DESCRIPTION

NO.

NAME

I/O

DESCRIPTION

AGND

9, 10, 26

−

Analog ground for digital/analog cells in core

AVCC

33

−

High-voltage analog power supply (8.5 V to 14 V)

AVDD

29

O

5-V Regulated output

AVDDREF

7

O

5-V Reference output—provided for connection to adjacent VREF terminal.

BSLN

13

I/O

Bootstrap I/O for left channel, negative high-side FET

BSLP

24

I/O

Bootstrap I/O for left channel, positive high-side FET

BSRN

48

I/O

Bootstrap I/O for right channel, negative high-side FET

BSRP

37

I/O

Bootstrap I/O for right channel, positive high-side FET

COSC

28

I/O

I/O for charge/discharging currents onto capacitor for ramp generator triangle wave biased at V2P5

FADE

30

I

Input for controlling volume ramp rate when cycling SD or during power-up. A logic low on this pin places

the amplifier in fade mode. A logic high on this pin allows a quick transition to the desired volume setting.

LINN

6

I

Negative differential audio input for left channel

LINP

5

I

Positive differential audio input for left channel

LOUTN

16, 17

O

Class-D 1/2-H-bridge negative output for left channel

LOUTP

20, 21

O

Class-D 1/2-H-bridge positive output for left channel

MUTE

34

I

A logic high on this pin disables the outputs. A low on this pin enables the outputs.

NC

31, 32,

35

−

Not internally connected

PGNDL

18, 19

−

Power ground for left channel H-bridge

PGNDR

42, 43

−

Power ground for right channel H-bridge

PVCCL

14, 15

−

Power supply for left channel H-bridge (tied to pins 22 and 23 internally), not connected to PVCCR or

AVCC.

PVCCL

22, 23

−

Power supply for left channel H-bridge (tied to pins 14 and 15 internally), not connected to PVCCR or

AVCC.

PVCCR

38,39

−

Power supply for right channel H-bridge (tied to pins 46 and 47 internally), not connected to PVCCL or

AVCC.

PVCCR

46, 47

−

Power supply for right channel H-bridge (tied to pins 38 and 39 internally), not connected to PVCCL or

AVCC.

REFGND

12

−

Ground for gain control circuitry. Connect to AGND. If using a DAC to control the volume, connect the DAC

ground to this terminal.

RINP

3

I

Positive differential audio input for right channel

RINN

2

I

Negative differential audio input for right channel

ROSC

27

I/O

Current setting resistor for ramp generator. Nominally equal to 1/8*VCC

ROUTN

44, 45

O

Class-D 1/2-H-bridge negative output for right channel

ROUTP

40, 41

O

Class-D 1/2-H-bridge positive output for right channel

SD

1

I

Shutdown signal for IC (low = shutdown, high = operational). TTL logic levels with compliance to VCC.

VCLAMPL

25

−

Internally generated voltage supply for left channel bootstrap capacitors.

VCLAMPR

36

−

Internally generated voltage supply for right channel bootstrap capacitors.

VOLUME

11

I

DC voltage that sets the gain of the amplifier.

VREF

8

I

Analog reference for gain control section.

V2P5

4

O

2.5-V Reference for analog cells, as well as reference for unused audio input when using single-ended

inputs.