Reset function, Figure 5 - power on reset timing, Figure 6 - reset timing – Quatech 802.11B/G User Manual

Page 32: Table 18 - reset timing, 0 reset function

Quatech, Inc.

Airborne Enterprise Module Databook

32

7/15/2010

100-8080-120

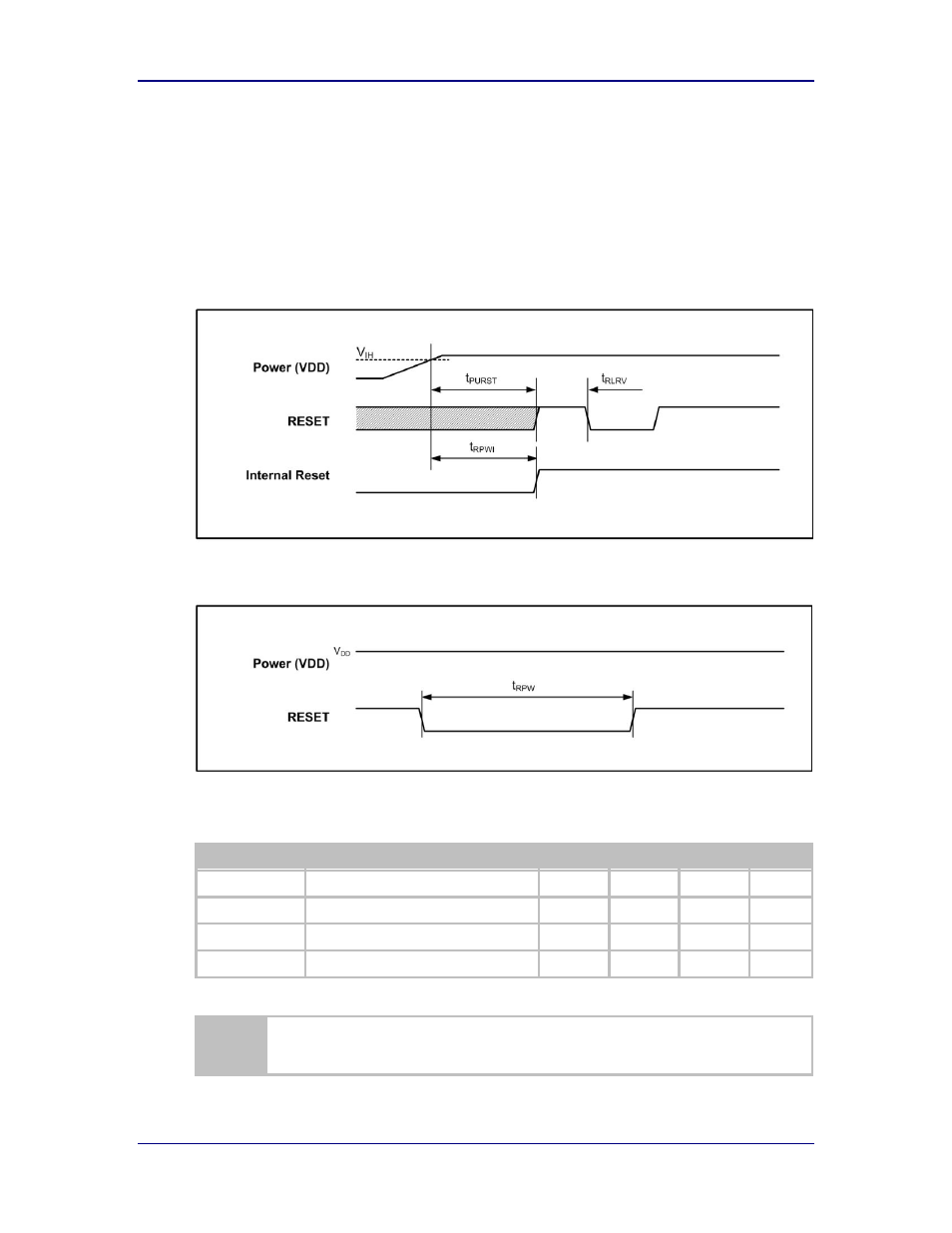

9.0 RESET Function

For correct operation of the on-board Power-on RESET (POR) and internal RESET

controllers, the RESET pin on the WLNG-XX-DP500 family must obey the following

timing and signal conditions.

Figure 5 - Power on RESET Timing

Figure 6 - RESET Timing

Table 17 - RESET Timing

Symbol

Parameter

Min

Typ

Max

Units

t

PURST

Valid V

DD

to RESET valid

200

ms

t

RLRV

RESET Valid to RESET Low

0

ms

t

RPWI

Valid V

DD

to Internal RESET completed

200

ms

t

RPW

RESET Pulse Width

100

µs

For Hardware revisions Rev C2 and earlier additional timing constraints apply. Please contact

Quatech Technical Support for details.