Connections – QSC Audio S series User Manual

Page 19

19

Connections:

Synchronizing the CobraNet Network to an AES/EBU Stream

Method 2: Use the recovered AES 48 kHz clock as an “external clock” source. When the jumper at header J37

is set to “AES”, the CobraNet interface uses the recovered 48 kHz clock at the first XLR connector (inputs 1 and

2) as the external synchronization clock. This method is similar to the “external synch” or “buddy link” mode of

clock distribution in which an external clock is applied to the “synch input” BNC connectors on the rear panel of

the RAVE. This method requires that the RAVE device be acting as the network conductor

and be configured for

external synchronization mode. External synchronization mode can be invoked by setting the left pair of

hexadecimal switches on the RAVE’s front panel to “80” or above. External synchronization can also be

configured through software via SNMP.

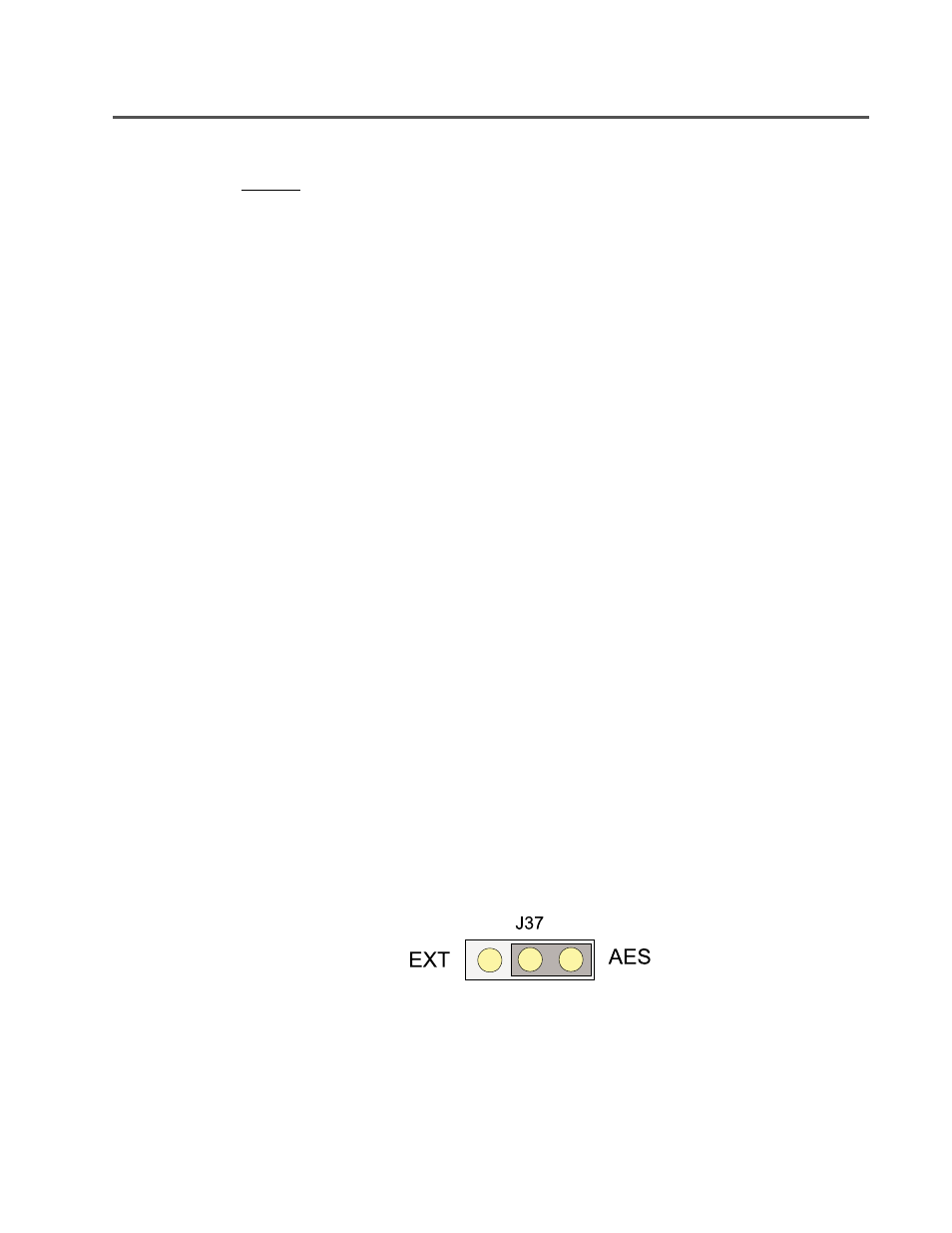

Header J37 is located toward the far left side of the RAVE PCB just above the power supply capacitors and to

the left of U137. The jumper configuration for implementing the “external clock” mode of AES synchronization is

shown below.

The advantage to implementing the “external clock” method of AES synchronization is that the on-board PLL is

still available should the RAVE lose the conductor role. This allows the RAVE device to function properly in the

performer role. When acting as the conductor, local audio clocks are derived from the master clock sourced by

the on-board PLL. The PLL is synchronized to an external clock, which happens to be the recovered 48 kHz clock

from the AES receiver at the channel 1 input.

The disadvantage to using the “external clock” method is that the unit must be configured for external synchro-

nization mode. Audio clocks are derived indirectly from the recovered 48 kHz AES stream.

It should be noted that external synchronization of the CobraNet network requires the on-board PLL. A RAVE

AES/EBU device acting as the system conductor, which is synchronizing to an external clock applied to the rear

panel “synch input”, must not have its jumper at header J39 configured for “AES clock”. This is a synchroniza-

tion violation since the device cannot track the external clock source.

SYNCHRONIZING TO AES/EBU