6 hardware information, 1 port addressing, 2 scratchpad / interrupt status register – Quatech QSP-200/300 User Manual

Page 41

6 Hardware Information

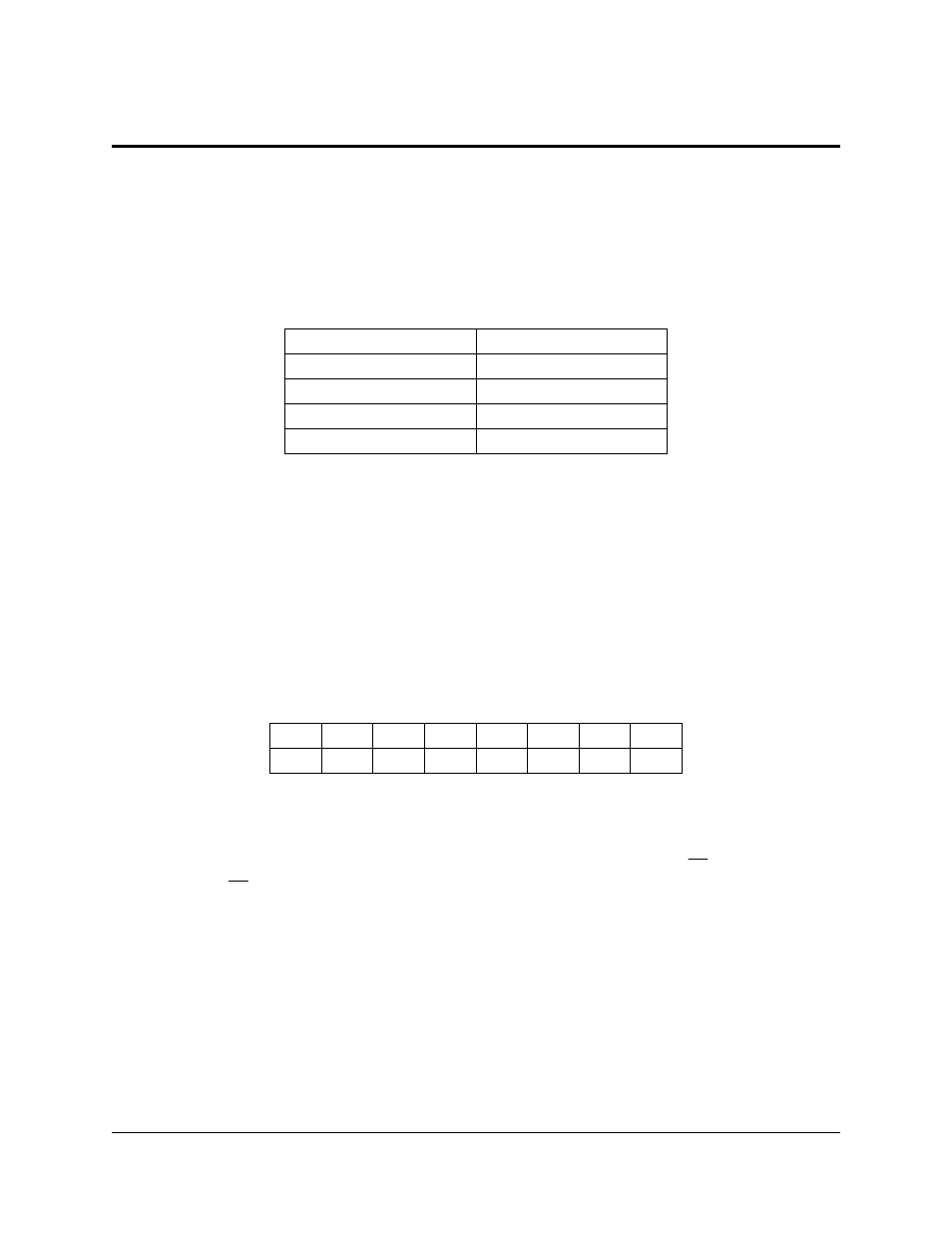

6.1 Port Addressing

The QSP-200/300's four asynchronous serial ports are implemented using 4 standard 16C550

UARTs. Each of these UARTs requires 8 bytes of I/O space and when enabled which requires

the QSP-200/300 to be located on an even 32-byte (20H) boundary (e.g. 300H, 320H, 340H,

etc.).

Base Address + 24

Channel D

Base Address + 16

Channel C

Base Address + 8

Channel B

Base Address + 0

Channel A

Address assignment

QSP-200/300 channel

6.2 Scratchpad / Interrupt Status Register

Each 16C550 UART contains 8 I/O registers. The last of these registers, located at (Base address

+ 7), is referred to as the 'Scratchpad Register' and provides no functionality to the UART. In

place of this Scratchpad Register, the QSP-200/300 implements an interrupt status register which

can be accessed at (Base address + 7) of any UART. The purpose of the interrupt status register

is to give the software programmer an easy way to inspect the interrupt state of the entire

QSP-200/300 with a single input operation. The format of the interrupt status register is shown

below:

Intr A

Intr B

Intr C

Intr D

0

0

0

0

D0

D1

D2

D3

D4

D5

D6

D7

When one or more UARTs have interrupts pending, the associated bit(s) in the interrupt status

register are set to logic 1. When all the pending interrupts have been serviced for a specific

UART, its interrupt status bit will be cleared to logic 0 automatically. When all the pending

interrupts from all UARTs have been serviced, the entire interrupt status register will return logic

0. The application program should not exit its interrupt service routine until all pending

interrupts from all channels have been serviced (interrupt status register = 0) or no additional

interrupts will be received.

If an application requires the UARTs' Scratchpad Registers, the interrupt status register can be

disabled. Disabling the interrupt status register is supported by the QSP-200/300 configuration

software, which is operating system dependent. Refer to the relevant operating system

installation section for specific usage of this feature.

QSP-200/300 User's Manual

35