Omega Speaker Systems PCI-DAS1001 User Manual

Page 29

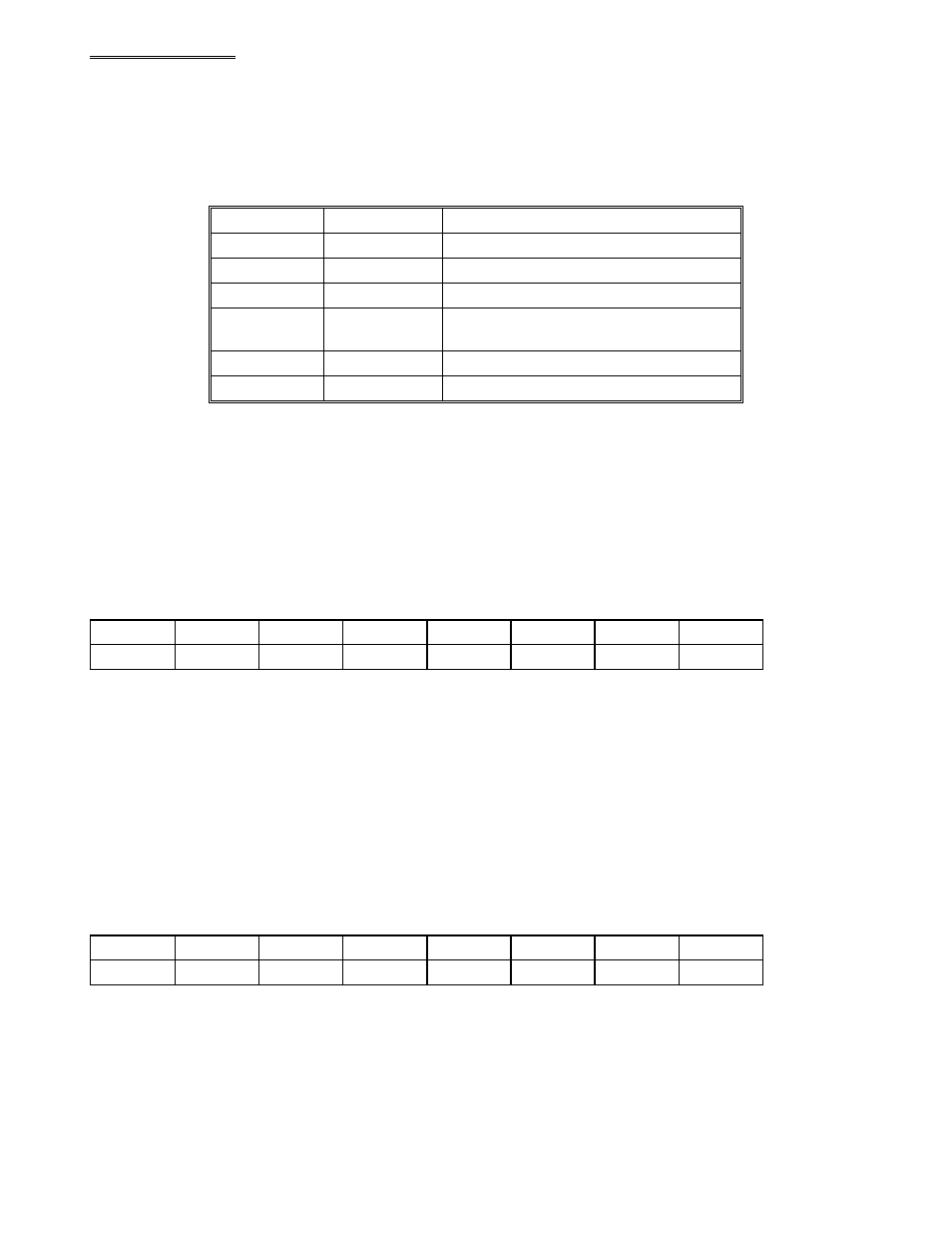

7.5 BADR3

The I/O Region defined by BADR3 contains data and control registers for the ADC Pacer, Pre/Post-Trigger Counters, User

Counters and Digital I/O bytes. The PCI-DAS1000 has two 8254 counter/timer devices. These are referred to as 8254A

and 8254B and are assigned as shown below:

User Counter #5

2

8254B

User Counter #4

1

8254B

User Counter #3 & ADC Pre-Trigger Index

Counter

0

8254B

ADC Pacer Upper Divider

2

8254A

ADC Pacer Lower Divider

1

8254A

ADC Post-Trigger Sample Counter

0

8254A

Function

Counter #

Device

All reads/writes to BADR3 are byte operations.

7.5.1 ADC PACER CLOCK DATA AND CONTROL REGISTERS

8254A COUNTER 0 DATA - ADC POST TRIGGER CONVERSION COUNTER

BADR3 + 0

READ/WRITE

D0

D1

D2

D3

D4

D5

D6

D7

0

1

3

2

4

5

6

7

Counter 0 is used to stop the acquisition when the desired number of samples have been gathered. It essentially is gated on

when a 'residual' number of conversions remain. The main counting of samples is done by the Interrupt Service Routine,

which will increment each time by 'packets' equal to 1/2 FIFO. Generally the value loaded into Counter 0 is N mod 1024,

where N is the total count, or the post trigger count, since Total count is not known when pre-trigger is active. Counter 0

will be enabled by use of the ARM bit (BADR1 + 4) when the next-to-last 1/2-full interrupt is processed. Counter 0 is to

operated in Mode 0.

8254A COUNTER 1 DATA - ADC PACER DIVIDER LOWER

BADR3 + 1

READ/WRITE

D0

D1

D2

D3

D4

D5

D6

D7

0

1

3

2

4

5

6

7

26