Omega Engineering DIGITAL INPUT/OUTPUT PCI-DIO96 User Manual

Page 19

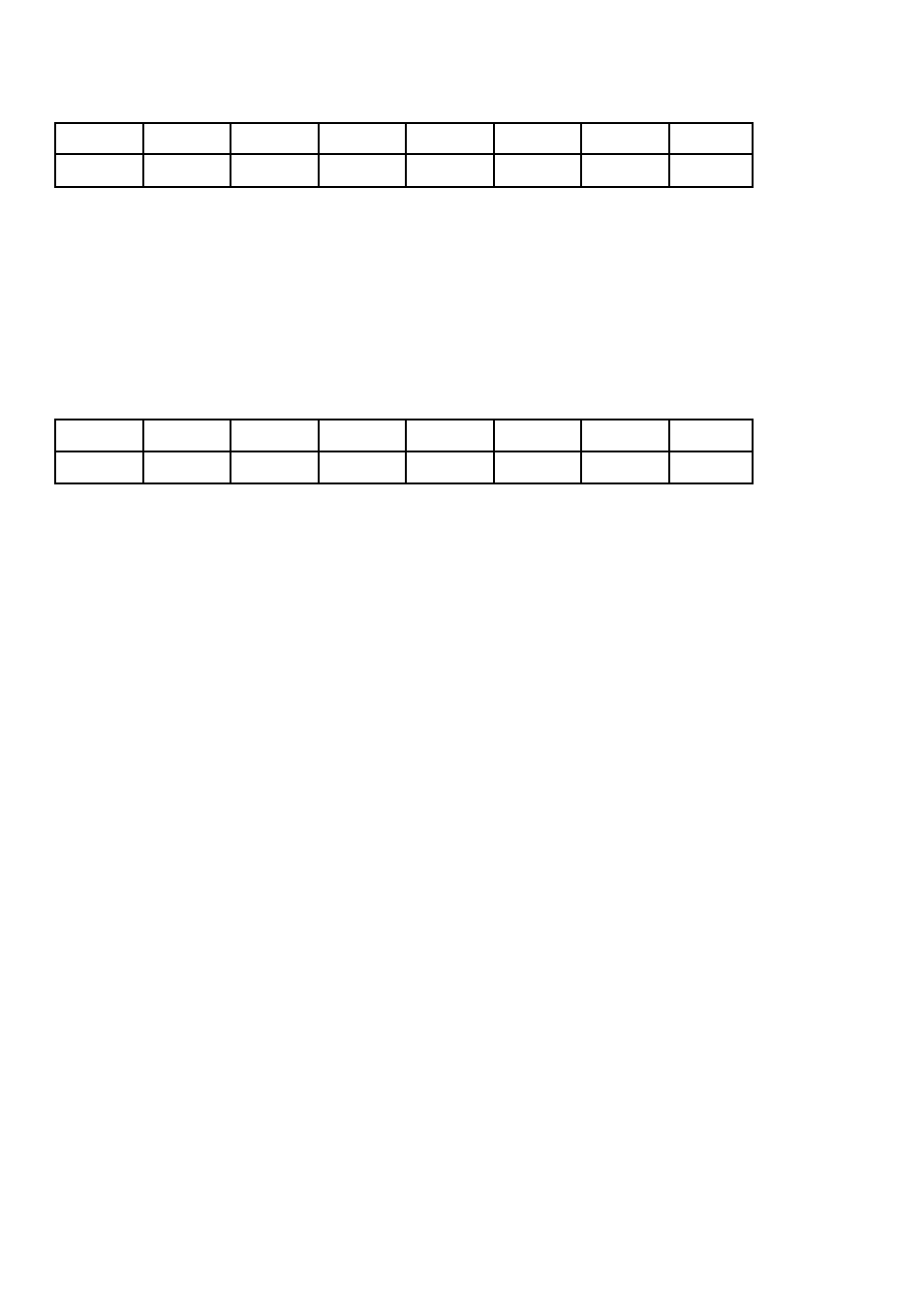

COUNTER CONFIGURATION

BADR3 + 13 hex

READ/WRITE

D0

D1

D2

D3

D4

D5

D6

D7

0

1

2

3

4

5

6

7

This register is used to set the operating modes of each of the 82C54’s counters.

Configure the counters by writing mode information to the Configure register,

followed by the count information written to the specific counter (data) registers.

Refer to the Celeritous 82C54 data sheets for more detailed information.

5.4.6

8255 Interrupt Source Configure

BADR3 + 14 hex

READ/WRITE

AIRQ0

AIRQ1

BIRQ0

BIRQ1

CIRQ0

CIRQ1

DIRQ0

DIRQ1

0

1

2

3

4

5

6

7

DIRQ1

When this bit is set, the 8255 in Group 3 will generate an interrupt on

INTRB if INTEN in BASE +15 hex is also set.

DIRQ0

When this bit is set, the 8255 in Group 3 will generate an interrupt on

INTRA if INTEN in BASE +15 hex is also set.

CIRQ1

When this bit is set, the 8255 in Group 2 will generate an interrupt on

INTRB if INTEN in BASE +15 hex is also set.

CIRQ0

When this bit is set, the 8255 in Group 2 will generate an interrupt on

INTRA if INTEN in BASE +15 hex is also set.

BIRQ1

When this bit is set, the 8255 in Group 1 will generate an interrupt on

INTRB if INTEN in BASE +15 hex is also set.

BIRQ0

When this bit is set, the 8255 in Group 1 will generate an interrupt on

INTRA if INTEN in BASE +15 hex is also set.

AIRQ1

When this bit is set, the 8255 in Group 0 will generate an interrupt on

INTRB if INTEN in BASE +15 hex is also set.

AIRQ0

When this bit is set, the 8255 in Group 0 will generate an interrupt on

INTRA if INTEN in BASE +15 hex is also set.

16