4 badr3 – Omega Engineering DIGITAL INPUT/OUTPUT PCI-DIO96 User Manual

Page 14

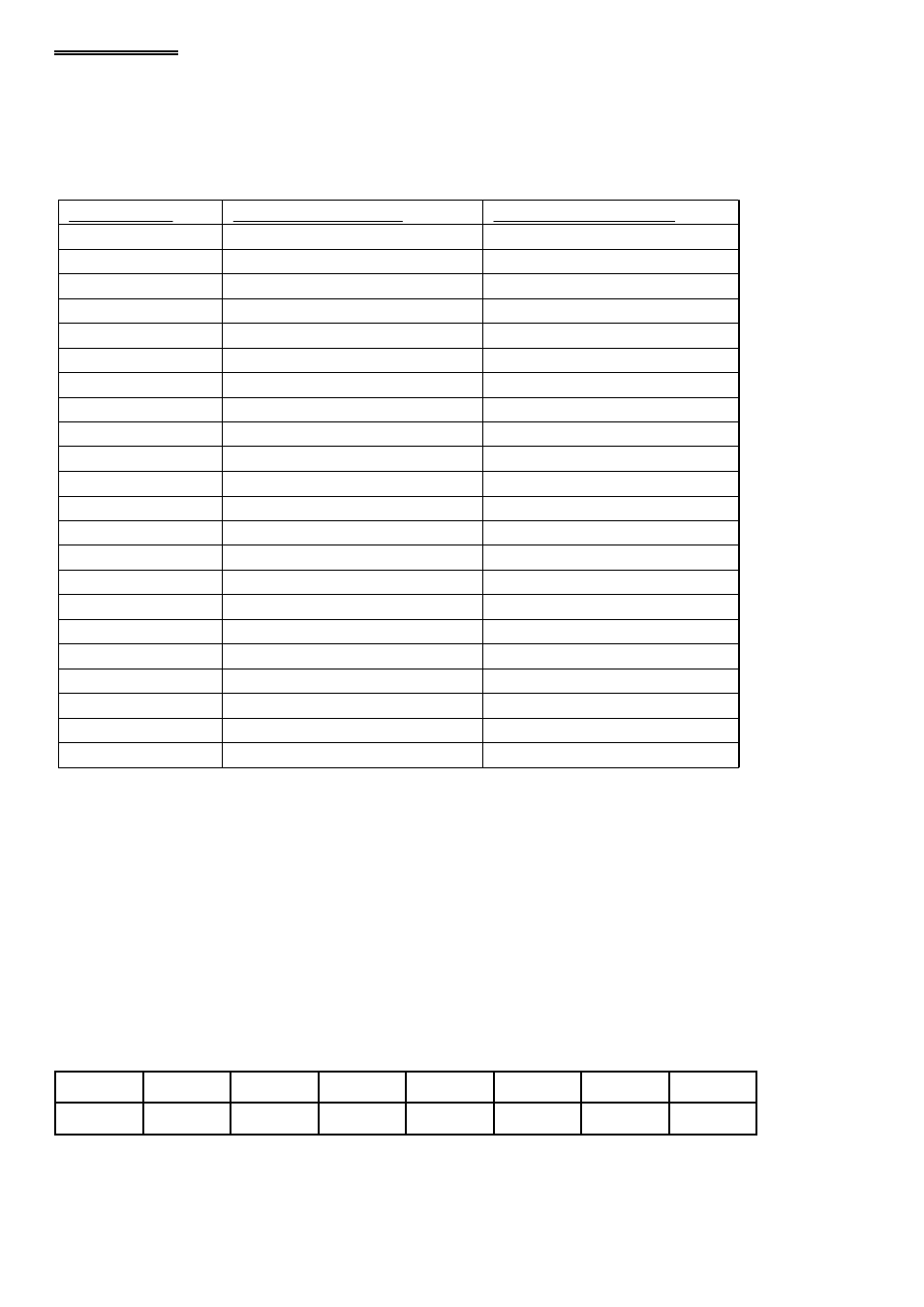

5.4 BADR3

BADR3 is an 8-bit data bus for reading, writing and control of the individual 82C55

chips and the 82C54. Refer to Table 5-2 for register offsets.

Table 5-2. BADR3 Registers

Interrupt Control 2

Interrupt Control 2

BADR3 + 15h

Interrupt Control 1

Interrupt Control 1

BADR3 + 14h

Counter Configure

Counter Configuration

BADR3 + 13h

N/A

N/A

BADR3 + 12h

Counter 2

Counter 2

BADR3 + 11h

Counter 1

Counter 1

BADR3 + 10h

Group 3 Configure

Group 3 Configure

BADR3 + F

Group 3 Port C Data

Group 3 Port C Data

BADR3 + E

Group 3 Port B Data

Group 3 Port B Data

BADR3 + D

Group 3 Port A Data

Group 3 Port A Data

BADR3 + C

Group 2 Configure

Group 2 Configure

BADR3 + B

Group 2 Port C Data

Group 2 Port C Data

BADR3 + A

Group 2 Port B Data

Group 2 Port B Data

BADR3 + 9

Group 2 Port A Data

Group 2 Port A Data

BADR3 + 8

Group 1 Configure

Group 1 Configure

BADR3 + 7

Group 1 Port C Data

Group 1 Port C Data

BADR3 + 6

Group 1 Port B Data

Group 1 Port B Data

BADR3 + 5

Group 1 Port A Data

Group 1 Port A Data

BADR3 + 4

Group 0 Configure

Group 0 Configure

BADR3 + 3

Group 0 Port Data

Group 0 Port C Data

BADR3 + 2

Group 0 Port B Data

Group 0 Port B Data

BADR3 + 1

Group 0 Port A Data

Group 0 Port A Data

BADR3 + 0

WRITE FUNCTION

READ FUNCTION

REGISTER

The 82C55 may be programmed to operate in Input/Ouput (mode 0), Strobed

Input/Ouput (mode 1) or Bi-Directional Bus (mode 2). The following information

describes mode 0 operation. Users needing information regarding other modes of

operation should refer to an Intel or Intersil 82C55 data sheet.

Upon power-up, an 82C55 is reset and defaults to the input mode. No further

programming is needed to use the 24 lines of an 82C55 as TTL inputs.

5.4.1

Group 0 8255 Configuration & Data

GROUP 0, PORT A DATA

BADR3 + 0

READ/WRITE

D0

D1

D2

D3

D4

D5

D6

D7

0

1

2

3

4

5

6

7

11