Renesas M65881AFP User Manual

Page 16

Rev.1.00 2003.05.08 page 16 of 23

M65881AFP

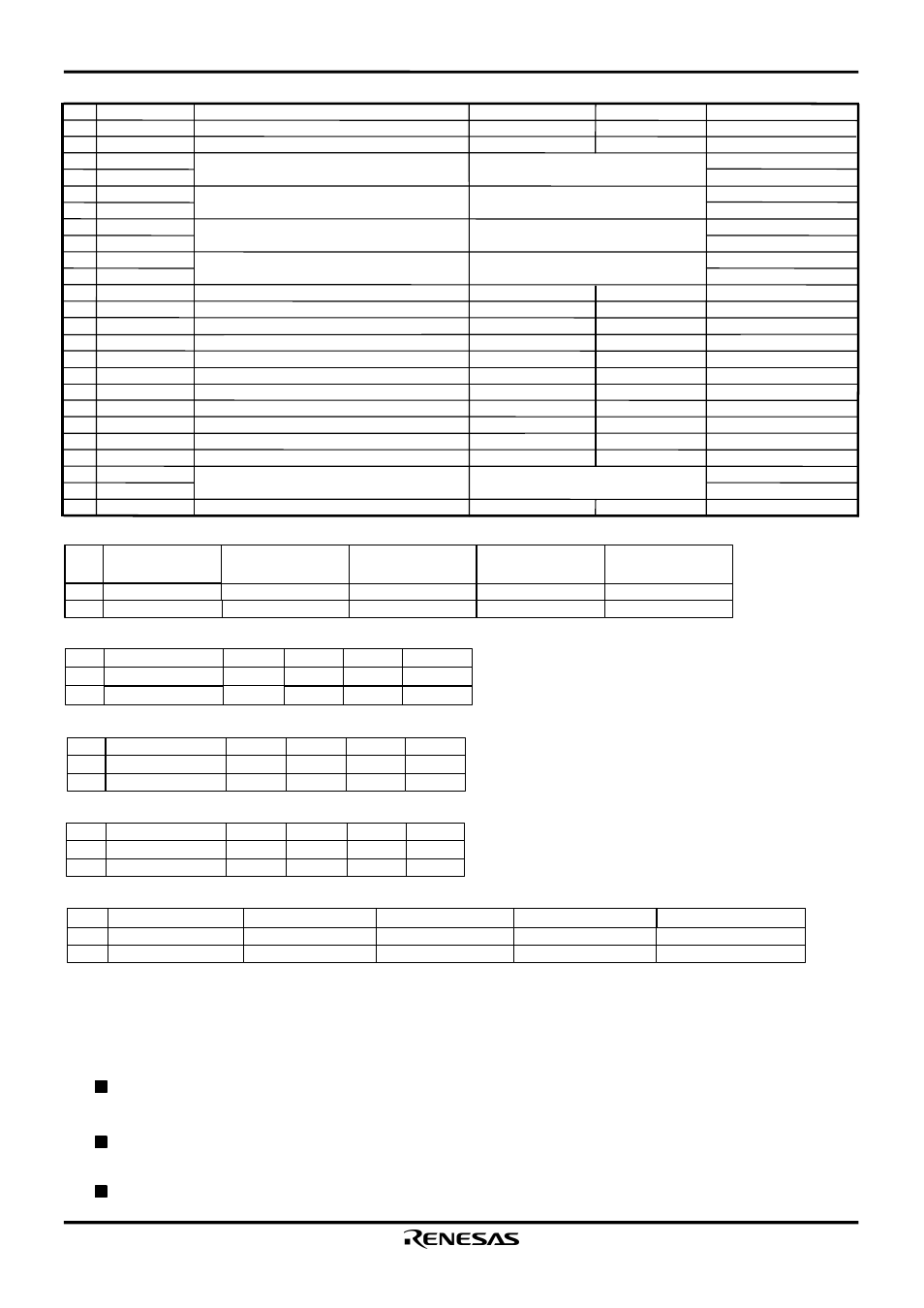

Table 2-1 Selection of input format

Table 2-2 Setting for Input Data Word Length

Table 2-3 Selection of Input Sampling Rate (fsi:32k to 48kHz, 2fsi:64k to 96kHz, and 4fsi:128k to 192kHz)

Table 2-4 Fs selection for De-emphasis filter (De-emphasis is "ON" except for bit9=L and bit10=L)

24bit

Don't use

20bit

bit

Flag Name

H

H

L

IBIT0

L

H

H

IBIT1

fsi

4fsi

2fsi

bit

Flag Name

L

L

H

H

7

ISF0

L

H

H

L

8

ISF1

bit

Flag Name

3

IFMT0

L

L

4

IFMT1

H

L

L

H

H

H

MSB First Left

Justified

MSB First Right

Justified

LSB First Right

Justified

I

2

S

48.0k

44.1k

bit

Flag Name

H

L

9

EMPFS1

L

H

10

EMPFS2

OFF

L

L

Don`t use

2. System1 Mode

No setting bits means "Don't care".

bit

Flag name

Function Explanation

H

L

INIT

1

MODE1

Mode Setting 1

"L" fixed

–

2

MODE2

Mode Setting 2

"H" fixed

–

3

IFMT0

L

4

IFMT1

L

5

IBIT0

L

6

IBIT1

L

7

ISF0

L

8

ISF1

L

9

EMPFS1

L

10 EMPFS2

L

11 DF1IMUTE

Zero Mute at DATA input

active

non-active

L

12 DF2IMUTE

Zero Mute at sampling rate converter input

active

non-active

L

13

–

14

–

15

–

16

–

17

–

18

–

19

–

20

ASYNC1MODE Asynchronous Detection Flag for Primary Side

Zero Mute

PWM:duty50%

L

21

–

22 PWMMODE0 Selection for PWM Output type

L

23 PWMMODE1

L

24 PWMHP

Phase of HPOUTL1/R1 based on PWM output for power

Same Phase

Reverse Phase

L

Refer to the Table2-1 below

Refer to the Table2-5 below

Refer to the Table2-2 below

Refer to the Table2-3 below

Refer to the Table2-4 below

Input Format Selection

Setting for Input Word Length

Input sampling rate selection

Fsi selection for De-emphasis Filter

16bit

L

L

32.0k

H

H

5

6

Table 2-5 Selection PWM Output

•PWM Output Form2 enables to operate following conditions.

MCKSEL=L ( Secondary master clock 1024fso )

Serial Control System2 Mode; bit16 ( NSOBIT ) = "H" ( 5bit )

bit 17 ( NSSPEED )="L" (16fso )

In case of the setting and release for PWM Output Form 2,

Refer to "The NOTE1 at setting PWM output Form 2" on next page.

bit

Flag name

22

PWMMODE0

23

PWMMODE1

PWM Output Form1

PWM Output Form3

PWM Output Form2

L

L

H

L

H

L

PWM Output Form4

H

H

Selection of Input format ( bit3,4: IFMT0,1)

Refer to Table 2-1.

Input word length (bit5,6: IBIT0,1)

Refer to Table 2-2. This setting is enable the case of MSB First Right justified.

Selection of Input Sampling Rate (bit7,8 : ISF0,1)

Refer to Table 2-3