Renesas M65881AFP User Manual

Renesas Receivers and Amplifiers

Rev.1.00 2003.05.08 page 1 of 23

Digital Amplifier Processor of S-Master* Technology

M65881AFP

REJ03F0004-0100Z

Rev.1.00

2003.05.08

DESCRIPTION

The M65881AFP is a S-Master technique processor for digital amplifier enable to convert from multi liner-PCM digital input signal

to high precise switching-pulse digital output without analog processing.

The M65881AFP has built-in 24bit sampling rate converter and digital-gain-controller.

The M65881AFP enables to realize high precise ( X`tal oscillation accuracy.) full digital amplifier systems combining with power

driver IC.

FEATURES

•Built-in 24bit Sampling Rate Converter.

Input Signal Sampling Rate from 32KHz to 192KHz (24bit Maximum).

4 kinds of Digital Input Format.

•Built-in L/R Independent Digital Gain Control.

•Built-in Soft Mute Function with Exponential Approximate-Curve.

•Correspondence to Output for Headphone.

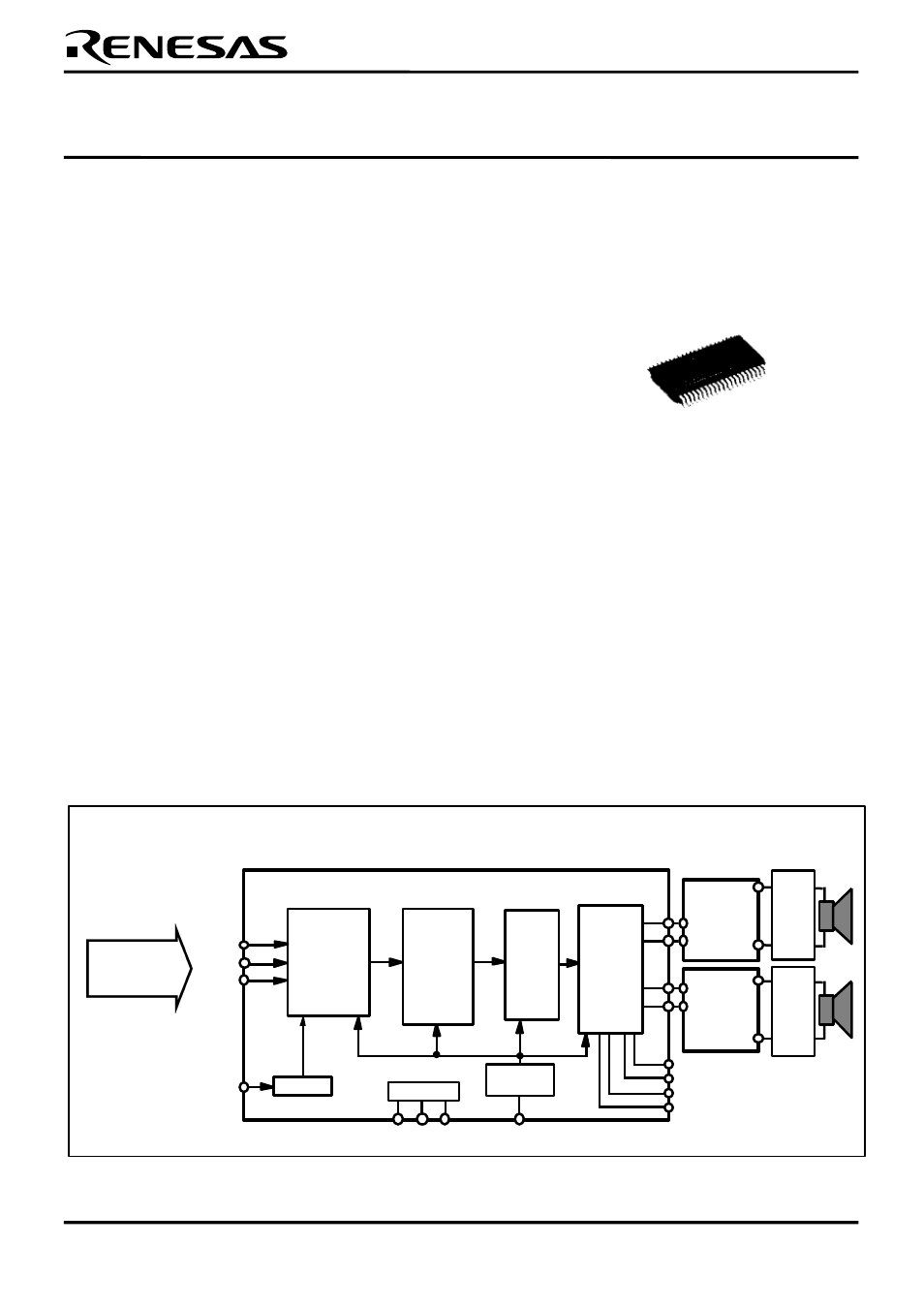

SYSTEM BLOCK DIAGRAM)

APPLICATION

DVD Receiver, AV Amplifier

RECOMMENDED OPERATING CONDITIONS

Logic Block:1.8V±10%,PWM Buffer Block :3.3V±10%

MAIN SPECIFICATION

•Master Clock

Primary Clock: 256Fsi/512Fsi Secondary Clock: 1024Fso/512Fso

•Input Signal Format:

MSB First Right Justified(16/20/24bit),MSB First Left Justified(24bit)

LSB First Right Justified(24bit),I

2

S(24bit)

•Input Signal Sampling Rate from 32kHz to 192kHz.

•Gain Control Function:

+30dB~-

∞

dB (0.1dB Step until -96dB, -138dB Minimum)

•Third Order

∆Σ

(16Fso:6bit/5bit,32Fso:5bit)

* "S-Master" is the digital amplifier technology developed by Sony Corporation. "S-Master" is a trademark of Sony Corporation.

Sampling

Rate

Converter

Clock

Stream

Power

Driver

LRCK

BCK

DATA

256fsi/512fsi

MCU I/F

M65881AFP

Level

Control

+30dB

to

-

∞

24bit

32kHz

to

192kHz

∆Σ

LC

Filter

LC

Filter

Stream

Power

Driver

1024fso/512fso

CD

DVD Audio

etc.

PWM

Clock

Output

for Headphone

OUTLINE : 42P2R

0.8mm pitch 42pin SSOP