Pinning, Agc circuit, Sound circuit – Philips TDA8303A User Manual

Page 5: Vertical synchronization, Modes of operation

July 1992

5

Philips Semiconductors

Preliminary specification

Small signal combination IC for black/white

TV

TDA8303

TDA8303A

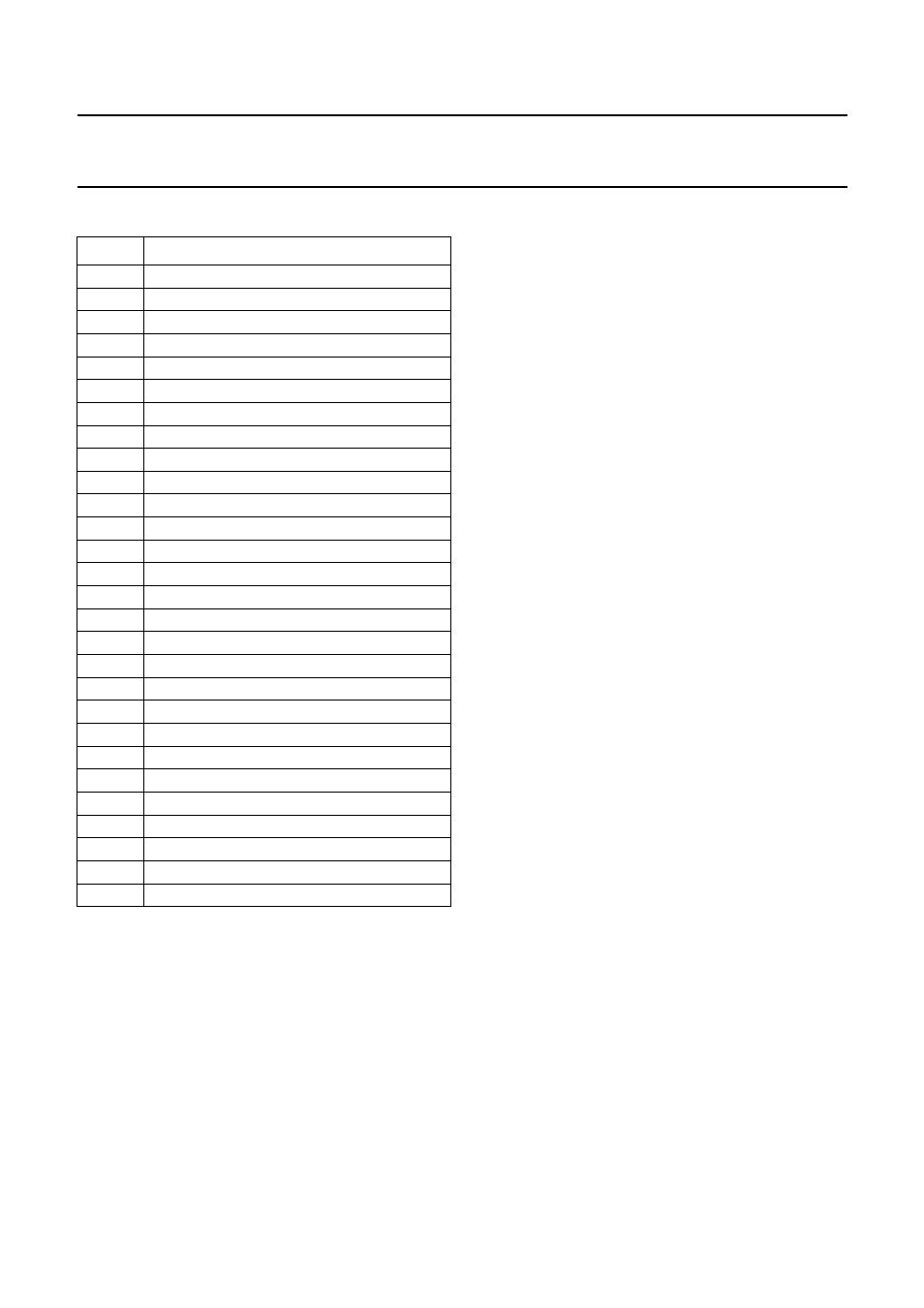

PINNING

AGC circuit

The AGC circuit of the TDA8303/TDA8303A is a top-sync

detector. The video signal coming from the video amplifier

passes a 2nd order low-pass filter before it is compared

with an internal reference level. The comparator stage is

gated when the horizontal oscillator is synchronized with

the video signal, such that interference pulses outside the

gating time have no influence on the gain control.

PIN

DESCRIPTION

1

AGC take-over

2

vertical ramp generator

3

vertical drive

4

vertical feedback

5

tuner AGC

6

ground

7

supply voltage input

8

video IF input

9

video IF input

10

IF AGC

11

volume control/start horizontal oscillator

12

audio output

13

sound demodulator

14

sound IF decoupling

15

sound IF input

16

ground (for some critical parts)

17

video amplifier output

18

AFC output

19

AFC S/H, AFC switch

20

video demodulator tuned circuit

21

video demodulator tuned circuit

22

coincidence detector

23

horizontal oscillator

24

phase 1 detector

25

sync separator input

26

horizontal drive output

27

horizontal flyback input

28

phase 2 detector

Sound circuit

The sound quality of the TDA8303/TDA8303A compared

with the predecessors has been improved at weak signal

conditions. The improvement has been achieved by the

new IF amplifier which is less sensitive for radiation from

the sound IF amplifier and by change of the ground and

supply connections in the IC. When out-of-sync condition

is detected by the coincidence detector the sound output

is muted. When no mute is required the minimum voltage

level on pin 22 should be clamped to a high level of 5 V.

At this level the gating of the AGC is switched off and the

phase 1 detector has a high output current for reliable

catching of a new transmitter.

Vertical synchronization

The TDA8303/TDA8303A embodies a synchronized

divider system for generating the vertical sawtooth at pin 2

having several advantages and features such as:

•

The vertical frequency is alignment free. The divider

automatically adapts to a vertical frequency of 50 Hz or

60 Hz including automatic amplitude correction and its

operating modes offer maximum

interference/disturbance protection.

•

A discriminator-window checks the accuracy of the

vertical trigger pulse. Internally clock pulses are

generated by doubling the line frequency. The divider

operates in the 60 Hz mode when the trigger pulse

appears before count 576, otherwise the 50 Hz mode

will be active.

•

The divider system operates with two different reset

windows for maximum interference/disturbance

protection. The windows are activated via an up/down

counter. The counter increases its counter-value by 1 for

each time the separated vertical sync pulse appears

within the selected window, otherwise the counter value

is decreased by 1.

Modes of operation

Large search window: divider ratio between 488 and 576.

This mode is valid for the following conditions:

•

Divider is looking for a new transmitter

•

Divider ratio found does not comply with the narrow

window specification limits

•

Up/down counter value of the divider system, operating

in the narrow window mode, drops below count 10