Table 3.23 phy resets, 6 detecting power management events, Figure 3.29 wake event detection block diagram – SMSC LAN9420 User Manual

Page 80: Phy resets, Detecting power management events, Fer to, Section 3.7.6, "detecting, Note 3.11, Note 3.10, Datasheet

Single-Chip Ethernet Controller with HP Auto-MDIX Support and PCI Interface

Datasheet

Revision 1.22 (09-25-08)

80

SMSC LAN9420/LAN9420i

DATASHEET

Note 3.10 PHY register bits designated as NASR are not initialized by setting the

bit

in the PHY’s

Note 3.11

PHY reset conditions and mode settings are discussed in

Section 3.7.5.1, "PHY Resets,"

3.7.5.1

PHY Resets

In addition to the PHY_RST, PHY_SRST and PCInRST noted in

, the PHY may also be reset

on specific state transitions depending on the state of the VAUXDET signal and

bit in the

PCI Power Management Control and Status Register (PCI_PMCSR)

. Resets may

leave the PHY in normal operating mode (all-capable with auto-negotiation enabled) or in the General

Power-Down mode. Specific PHY reset conditions and the state of the PHY following reset, are

detailed in

below. The state transitions noted in this table refer to those specified in

3.7.4, "Power States," on page 75

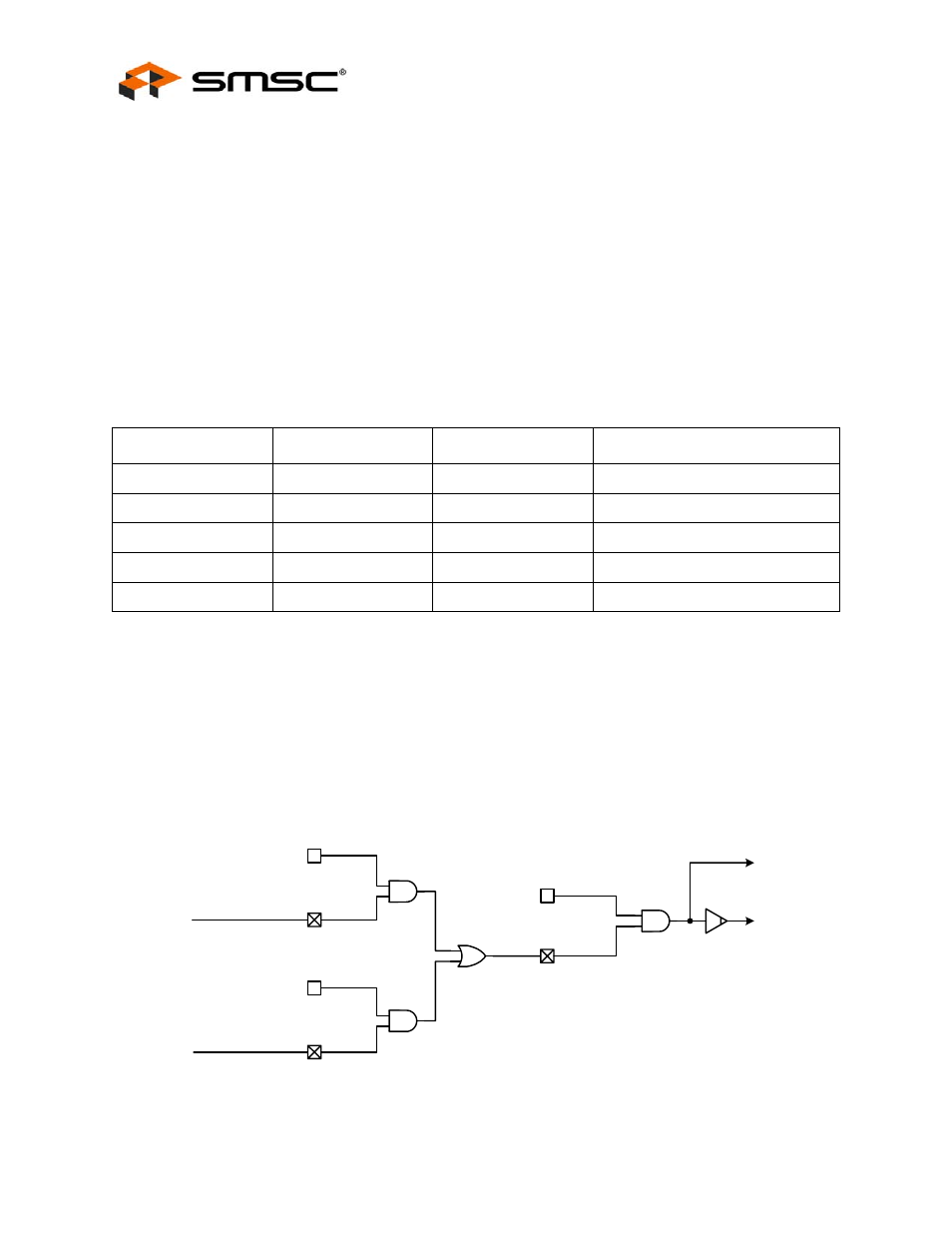

3.7.6

Detecting Power Management Events

LAN9420/LAN9420i supports the ability to generate PCI wake events using nPME on detection of a

Magic Packet, Wakeup Frame or Ethernet link status change (energy detect). A simplified diagram of

the wake event detection logic is shown in

Table 3.23 PHY Resets

CONDITION

VAUXDET

PME_EN

MODE

T9

0

X

Normal

T6

1

X

General Power-Down

T1, T3

X

0

General Power-Down

T10, T11

1

0

General Power-Down

T5 (D3RST)

X

0

Normal

Figure 3.29 Wake Event Detection Block Diagram

MAC Wakeup

Event

WOL_EN

(PMT_CTRL Register)

RW

WUPS[1]

(PMT_CTRL Register)

PHY Interrupt

ED_EN

(PMT_CTRL Register)

RW

WUPS[0]

(PMT_CTRL Register)

PME_STATUS

(PCI_PMCSR Register)

PME_EN

(PCI_PMCSR Register)

RW

nPME

(PCI Bus)

WAKE_INT

(Interrupt Controller)