Function block diagram, Datasheet, Ddr3 sdram – Samsung M471B1G73AH0 User Manual

Page 8: Unbuffered sodimm, Rev. 1.0

- 8 -

Unbuffered SODIMM

datasheet

DDR3 SDRAM

Rev. 1.0

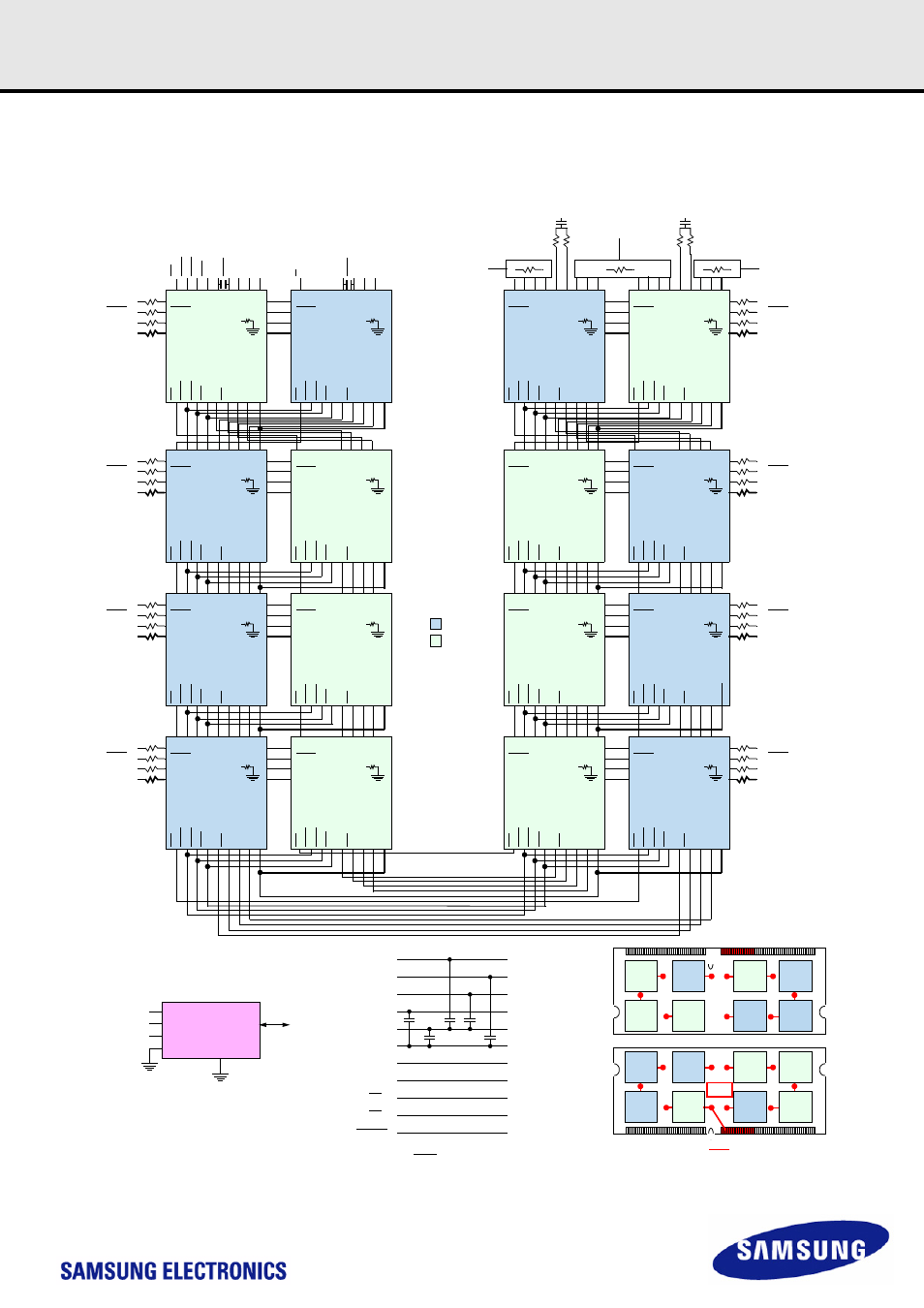

7. Function Block Diagram:

7.1 8GB, 1Gx64 Module (Populated as 2 ranks of x8 DDR3 SDRAMs)

V7

V8

V5

S1 RA

S

CA

S

WE CK

1

CK

1

C

KE1

ODT1

A[0

:N

]

/BA

[0:N]

S

0

CK

0

CK

0

C

KE0

ODT0

DQS3

DQS3

DM3

DQS

DQS

D11

CS RA

S

CA

S

WE CK

CK CK

E

OD

T

A

[N

:0]

/BA[

N:

0]

ZQ

DQ[0:7]

DM

240

Ω

±

1%

DQ[24:31]

D3

CS RA

S

CA

S

WE CK

CK CK

E

OD

T

A

[N

:0]

/BA[

N:

0]

ZQ

240

Ω

±

1%

Vtt

V

DD

Vtt

Rank0

Rank1

NOTE :

1. DQ wiring may differ from that shown however ,DQ, DM, DQS and DQS relationships are maintained as shown

V

SS

V

DD

D0 - D15

V

REFCA

V

DDSPD

SPD

CK0

V

REFDQ

D0 - D15

D0 - D15

D0 - D15, SPD

V

tt

CK1

CK0

CK1

RESET

V

tt

D8 - D15

D0 - D7

D0 - D7

D8 - D15

D0 - D7

V6

V2

V3

D6

D12

D3

D9

V

tt

Address and Controllines

DQS

DQS

DQ[0:7]

DM

DQS1

DQS1

DM1

DQS

DQS

D1

CS RA

S

CA

S

WE CK

CK CK

E

ODT

A[N

:0

]/B

A[N

:0

]

ZQ

DQ[0:7]

DM

240

Ω

±

1%

DQ[8:15]

D9

CS RA

S

CA

S

WE CK

CK CK

E

ODT A[N

:0

]/B

A[N

:0

]

ZQ

240

Ω

±

1%

DQS

DQS

DQ[0:7]

DM

DQS0

DQS0

DM0

DQS

DQS

D0

CS RA

S

CA

S

WE CK

CK CK

E

ODT

A

[N:0]/B

A[N:0

]

ZQ

DQ[0:7]

DM

240

Ω

±

1%

DQ[0:7]

D8

CS RA

S

CA

S

WE CK

CK CK

E

ODT A

[N:0]/B

A[N:0

]

ZQ

240

Ω

±

1%

DQS

DQS

DQ[0:7]

DM

DQS2

DQS2

DM2

DQS

DQS

D2

CS RA

S

CA

S

WE CK

CK CK

E

ODT

A[

N:

0]/B

A[N

:0

]

ZQ

DQ[0:7]

DM

240

Ω

±

1%

DQ[16:23]

D10

CS RA

S

CA

S

WE CK

CK CK

E

ODT A[

N:

0]/B

A[N

:0

]

ZQ

240

Ω

±

1%

DQS

DQS

DQ[0:7]

DM

DQS

DQS

D4

CS RA

S

CA

S

WE CK

CK

CK

E

OD

T

A

[N

:0]

/BA[

N:

0]

ZQ

DQ[0:7]

DM

240

Ω

±

1%

D12

CS RA

S

CA

S

WE CK

CK CK

E

OD

T

A

[N

:0]

/BA[

N:

0]

ZQ

240

Ω

±

1%

DQS

DQS

DQ[0:7]

DM

DQS

DQS

D14

CS RA

S

CA

S

WE CK

CK

CK

E

ODT

A[N

:0

]/B

A[N

:0

]

ZQ

DQ[0:7]

DM

240

Ω

±

1%

D6

CS RA

S

CA

S

WE CK

CK CK

E

ODT

A[N

:0

]/B

A[N

:0

]

ZQ

240

Ω

±

1%

DQS

DQS

DQ[0:7]

DM

DQS

DQS

D15

CS RA

S

CA

S

WE CK

CK

CK

E

ODT

A

[N:0]/B

A[N:0

]

ZQ

DQ[0:7]

DM

240

Ω

±

1%

D7

CS RA

S

CA

S

WE CK

CK CK

E

ODT

A

[N:0]/B

A[N:0

]

ZQ

240

Ω

±

1%

DQS

DQS

DQ[0:7]

DM

DQS

DQS

D13

CS RA

S

CA

S

WE CK

CK

CK

E

ODT

A[

N:

0]/B

A[N

:0

]

ZQ

DQ[0:7]

DM

240

Ω

±

1%

D5

CS RA

S

CA

S

WE CK

CK CK

E

ODT

A[

N:

0]/B

A[N

:0

]

ZQ

240

Ω

±

1%

DQS

DQS

DQ[0:7]

DM

DQS4

DQS4

DM4

DQ[32:39]

DQS6

DQS6

DM6

DQ[48:55]

DQS7

DQS7

DM7

DQ[56:63]

DQS5

DQS5

DM5

DQ[40:47]

V

DD

D7

D5

D10

D8

V1

V4

V9

V7

V6

V9

V8

V4

V3

D15

D13

D2

D0

D14

D4

D11

D1

V1

V2

V5

V1

Vtt

A0

A1

A2

SA0

SA1

SCL

SDA

WP

SCL

(SPD)