Chapter 2 functional block diagram, Figure 2.1 usb3280 block diagram, Chapter 2 – SMSC USB3280 User Manual

Page 7: Functional block diagram, Datasheet, Utmi in te r fac e, 8v regulator

Hi-Speed USB Device PHY with UTMI Interface

Datasheet

SMSC USB3280

7

Revision 1.5 (11-15-07)

DATASHEET

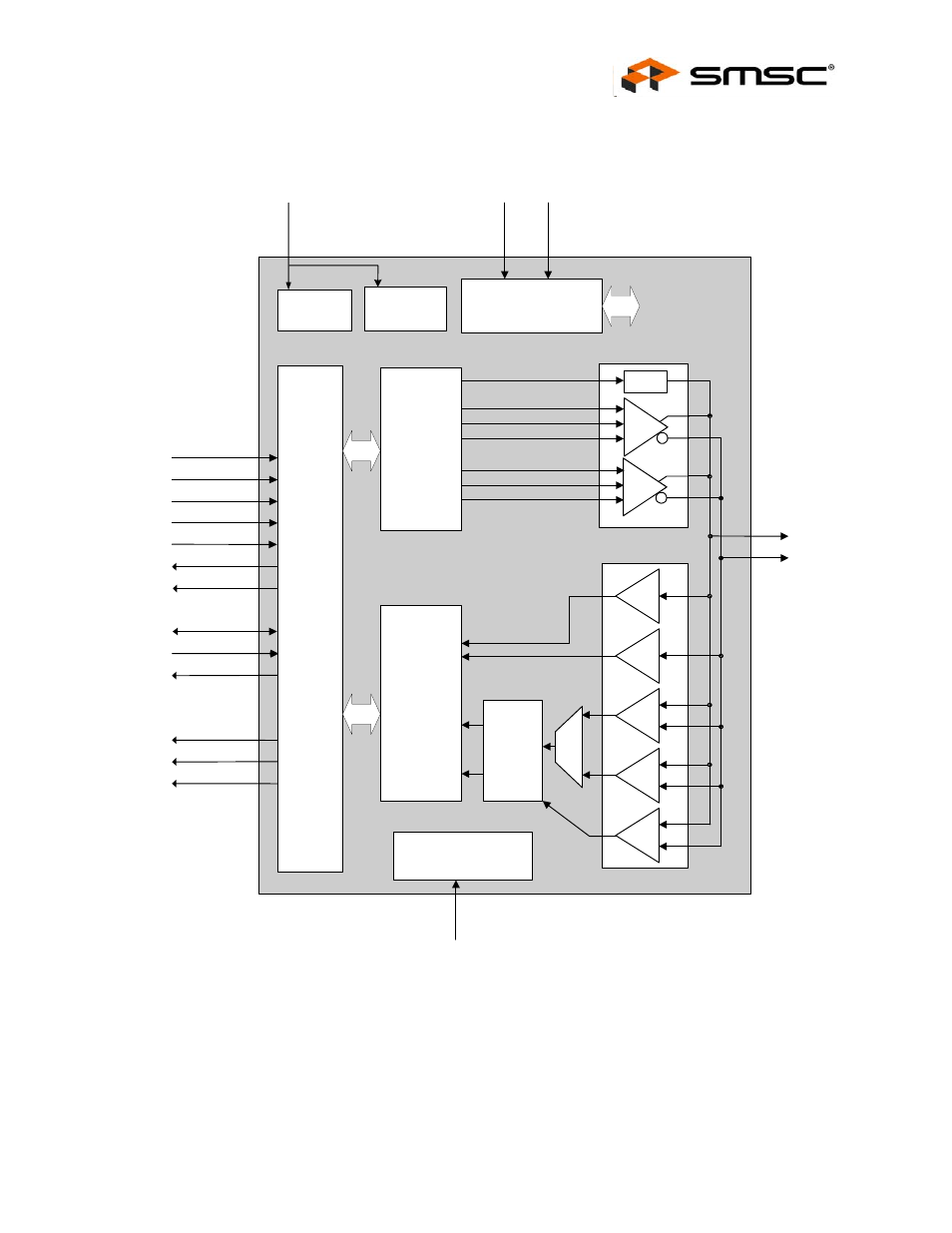

Chapter 2 Functional Block Diagram

Figure 2.1 USB3280 Block Diagram

PWR

Control

FS SE+

R

X

UTMI

In

te

r

fac

e

TX State

Machine

Parallel to

Serial

Conversion

Bit Stuff

NRZI

Encode

TX

LOGIC

Clock

Recovery Unit

Clock

and

Data

Recovery

Elasticity

Buffer

VP

VM

BIASING

Bandgap Voltage Reference

Current Reference

RB

IA

S

VD

D3

.3

PLL and

XTAL OSC

System

Clocking

FS RX

FS SE-

HS RX

HS SQ

RX State

Machine

Serial to

Parallel

Conversion

Bit Unstuff

NRZI

Decode

RX

LOGIC

DM

TX

1.5kΩ

FS

TX

HS

TX

HS_DATA

HS_CS_ENABLE

HS_DRIVE_ENABLE

OEB

VMO

VPO

RPU_EN

MU

X

DP

RXVALID

RXACTIVE

RXERROR

TXREADY

RESET

SUSPENDN

XCVRSELECT

TERMSELECT

OPMODE[1:0]

LINESTATE[1:0]

CLKOUT

TXVALID

DATA[7:0]

XI

XO

1.8V

Regulator