Table 3. j1 pin descriptions – Silicon Laboratories Network Card User Manual

Page 34

E t h e r n e t - D K

34

Rev. 0.6

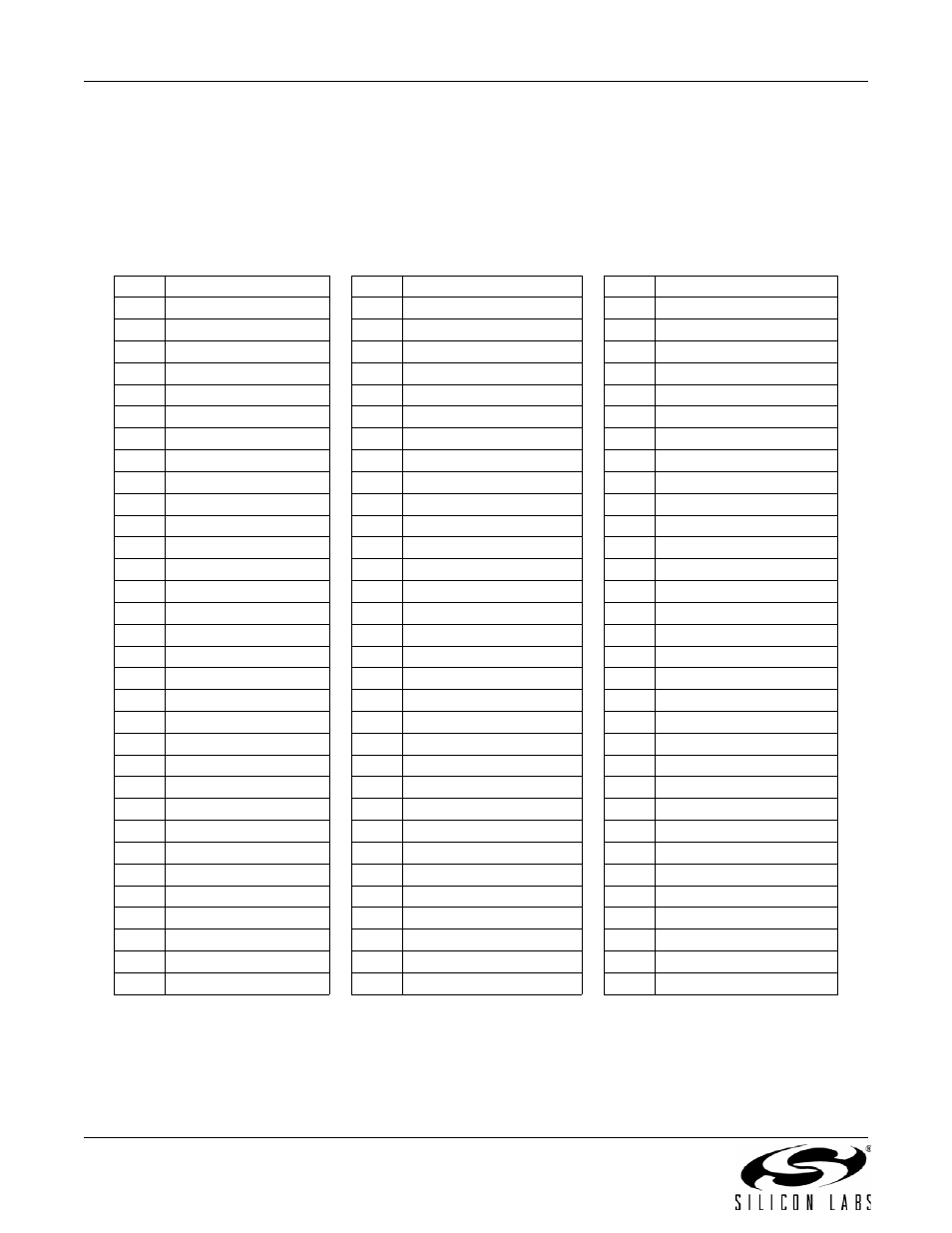

9.1. Expansion I/O Connector (J1)

The 96-pin expansion I/O connector J1 is used to connect the AB4 Ethernet Development Board to the C8051F120

Target Board. J1 provides access to many C8051F120 signal pins. Pins for +3 V, digital ground, analog ground and

the unregulated power supply (VUNREG) are also available. The VUNREG pin is connected directly to the

unregulated +V pin of the P1 power connector on the C8051F120 Target Board. See Table 3 for a complete list of

pins available at J1.

Table 3. J1 Pin Descriptions

Pin #

Description

Pin #

Description

Pin #

Description

A-1

+3 VD2 (+3.3 VDC)

B-1

DGND (Digital Gnd)

C-1

XTAL1

A-2

MONEN

B-2

P1.7

C-2

P1.6

A-3

P1.5

B-3

P1.4

C-3

P1.3

A-4

P1.2

B-4

P1.1

C-4

P1.0

A-5

P2.7

B-5

P2.6

C-5

P2.5

A-6

P2.4

B-6

P2.3

C-6

P2.2

A-7

P2.1

B-7

P2.0

C-7

P3.7

A-8

P3.6

B-8

P3.5

C-8

P3.4

A-9

P3.3

B-9

P3.2

C-9

P3.1

A-10

P3.0

B-10

P0.7

C-10

P0.6

A-11

P0.5

B-11

P0.4

C-11

P0.3

A-12

P0.2

B-12

P0.1

C-12

P0.0

A-13

P7.7

B-13

P7.6

C-13

P7.5

A-14

P7.4

B-14

P7.3

C-14

P7.2

A-15

P7.1

B-15

P7.0

C-15

P6.7

A-16

P6.6

B-16

P6.5

C-16

P6.4

A-17

P6.3

B-17

P6.2

C-17

P6.1

A-18

P6.0

B-18

P5.7

C-18

P5.6

A-19

P5.5

B-19

P5.4

C-19

P5.3

A-20

P5.2

B-20

P5.1

C-20

P5.0

A-21

P4.7

B-21

P4.6

C-21

P4.5

A-22

P4.4

B-22

P4.3

C-22

P4.2

A-23

P4.1

B-23

P4.0

C-23

TMS

A-24

TCK

B-24

TDI

C-24

TDO

A-25

/RST

B-25

DGND (Digital Gnd)

C-25

VUNREG

A-26

AGND (Analog Gnd)

B-26

DAC1

C-26

DAC0

A-27

CP1-

B-27

CP1+

C-27

CP0-

A-28

CP0+

B-28

VREF

C-28

VREFD

A-29

VREF0

B-29

VREF1

C-29

AIN0.7

A-30

AIN0.6

B-30

AIN0.5

C-30

AIN0.4

A-31

AIN0.3

B-31

AIN0.2

C-31

AIN0.1

A-32

AIN0.0

B-32

AGND (Analog Gnd)

C-32

AV+ (+3.3 VDC Analog)