1 event detector control, 2 address comparison setup – Motorola ONCE SC140 User Manual

Page 8

4

Using the SC140 Enhanced OnCE Stopwatch Timer

Initializing the stopwatch timer consists of setting up the Address Event Detection Channel (EDCA). The

role of EDCA in the stopwatch timer implementation is to trigger the commencement of the cycle

countdown. The Enhanced OnCE supports six EDCAs. The implementation presented in this application

note uses EDCA1, though this choice is arbitrary.

Set up of the EDCA requires initializing the following four registers:

•

The 32-bit EDCA reference value register A (EDCA1_REFA).

•

The 32-bit EDCA reference value register B (EDCA1_REFB).

•

The 32-bit EDCA mask register (EDCA1_MASK).

•

The 16-bit EDCA control register (EDCA1_CTRL).

3.1.1

Event Detector Control

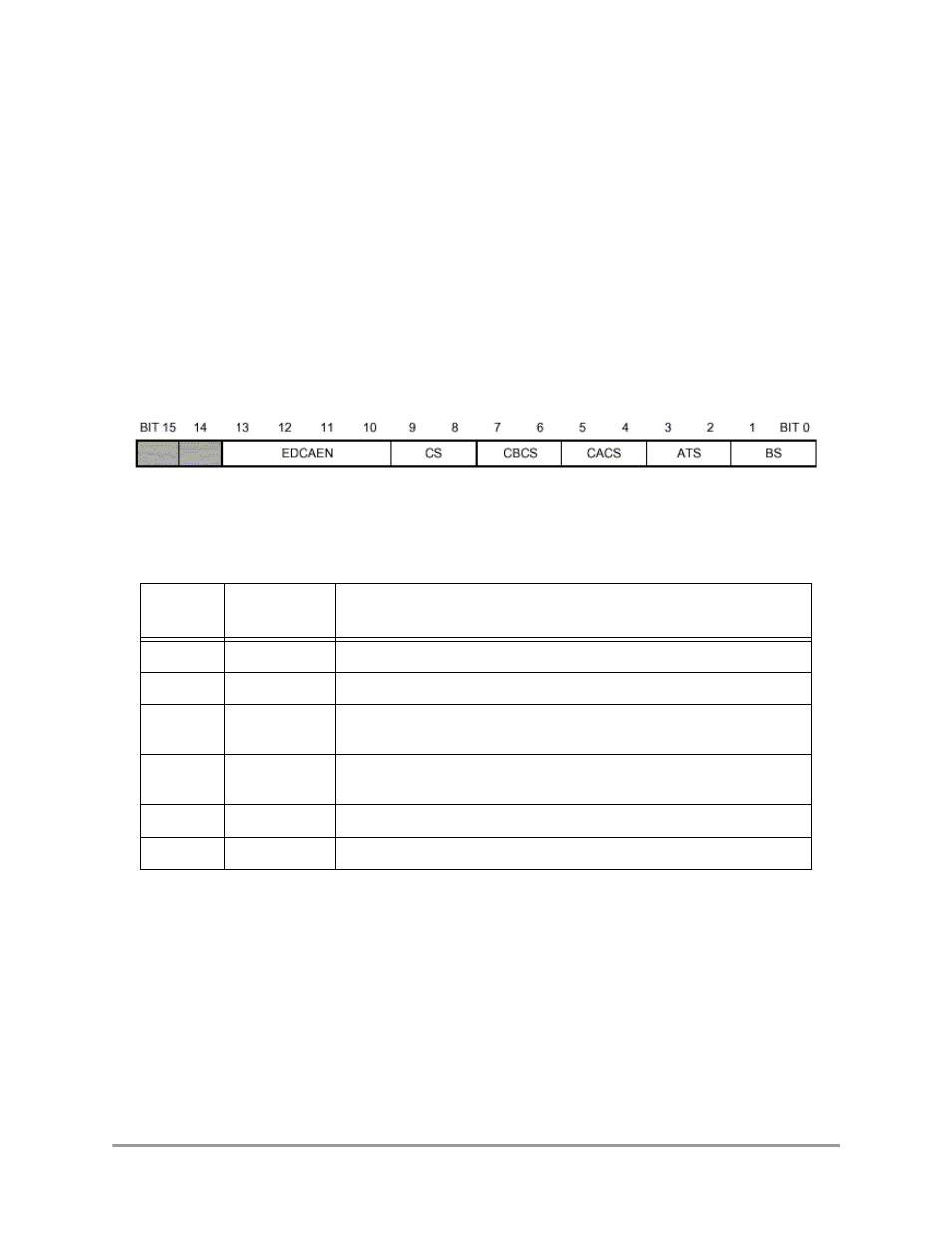

The register, EDCA1_CTRL, controls the behavior of the EDCA. The fields of the EDCA1_CTRL register

are shown in Figure 2.

Figure 2. EDCA Control Register (EDCA1_CTRL)

Table 1 describes the settings of these fields in the stopwatch timer implementation.

The EDCA becomes enabled as soon as these values are written into the control register. The EDCA stays

enabled for the duration of the program execution to enable repeated use of the stopwatch timer.

3.1.2

Address Comparison Setup

The purpose of the address comparison in the EDCA is to detect writes to the stopwatch timer flag

variable. Because writes may take place on either of the two data memory buses, both registers,

EDCA1_REFA and EDCA1_REFB, are set up to contain the address of the stopwatch timer flag variable.

The register EDCA1_MASK allows masking of address bits when comparing the sampled address with

those in the EDCA1_REFA and EDCA1_REFB registers. In the implementation of the stopwatch timer all

Table 1. EDCA_CTRL Settings

Field

Setting

(binary value)

Description

EDCAEN

1111

This channel is enabled

CS

11

Trigger event if address matches either comparator A or comparator B

CBCS

00

An “address match” is detected when sampled bus value equals value in

EDCA_REFB

CACS

00

An “address match” is detected when sampled bus value equals value in

EDCA_REFA

ATS

01

Detect write access only

BS

10

The sampled buses are XABA and XABB