Motorola MPC750 User Manual

Page 3

MOTOROLA

Errata to MPC750 UserÕs Manual

3

5.1.7, 5-18

Table 5-4, delete the second row in table (

lwarx

or

stwcx.

with W = 1).

7.2.5.2.1, 7-14

For ARTRY, change ÒTiming Comments,Ó ÒNegation,Ó Þrst paragraph,

last sentence to the following:

First the buffer goes to high impedance for a minimum of one-half

processor cycle (dependent on the clock mode), then it is driven

negated for one-half bus cycle before returning to high impedance.

9.1.2, 9-5

In Table 9-1, replace the description of L2CR[L2DO] (bit 9), with the

following:

11.2.1.5, 11-7

Replace Table 11-6 with the following:

9

L2DO L2 data-only. Setting this bit inhibits the caching of instructions in the L2

cache. All accesses from the L1 instruction cache are treated as

cache-inhibited by the L2 cache (bypass L2 cache, no L2 tag look-up

performed).

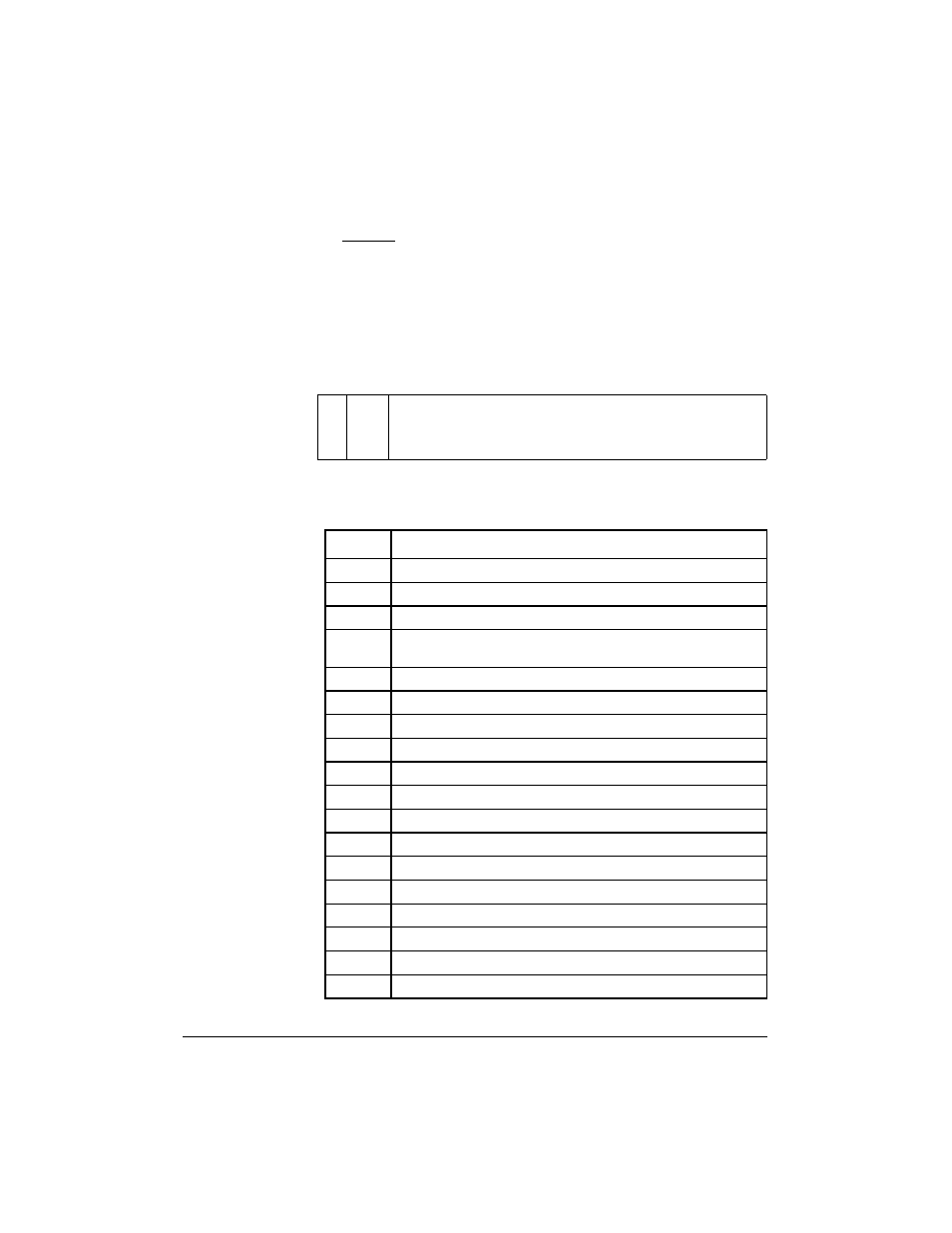

Table 11-16. PMC2 EventsÑMMCR0[26Ð31] Select Encodings

Encoding

Description

00 0000

Register holds current value.

00 0001

Counts processor cycles.

00 0010

Counts completed instructions. Does not include folded branches.

00 0011

Counts transitions from 0 to 1 of TBL bits speciÞed through

MMRC0[RTCSELECT]. 00 = 47, 01 = 51, 10 = 55, 11 = 63.

00 0100

Counts instructions dispatched. 0, 1, or 2 instructions per cycle.

00 0101

Counts L1 instruction cache misses.

00 0110

Counts ITLB misses.

00 0111

Counts L2 instruction misses.

00 1000

Counts branches predicted or resolved not taken.

00 1001

Counts MSR[PR] bit toggles.

00 1010

Counts times reserved load operations completed.

00 1011

Counts completed load and store instructions.

00 1100

Counts snoops to the L1 and the L2.

00 1101

Counts L1 cast-outs to the L2.

00 1110

Counts completed system unit instructions.

00 1111

Counts instruction fetch misses in the L1.

01 0000

Counts branches allowing out-of-order execution that resolved correctly.

All others

Reserved.