Motorola MPC750 User Manual

Page 2

2

Errata to MPC750 UserÕs Manual

MOTOROLA

Replace the description of HID0[BTIC] (bit 26), with the following:

2.1.2.4.5, 2-18

Replace Table 2-11 with the following:

4.5.11, 4-20

Remove Table 4-10, ÒTrace ExceptionÑSRR1 Settings.Ó This

interrupt is implemented as deÞned by the OEA. Remove the

Table 4-10 and the introductory text.

1

DBP

Disable 60x bus address and data parity generation.

0 The system generates address and data parity.

1 Parity generation is disabled and parity signals are driven to 0 during bus

operations. When parity generation is disabled, all parity checking should

also be disabled and parity signals need not be connected.

26 BTIC BTIC enable. Used to enable use of the 64-entry branch instruction cache.

0 The BTIC contents are invalidated and the BTIC behaves as if it were

empty. New entries cannot be added until the BTIC is enabled.

1 The BTIC is enabled and new entries can be added.

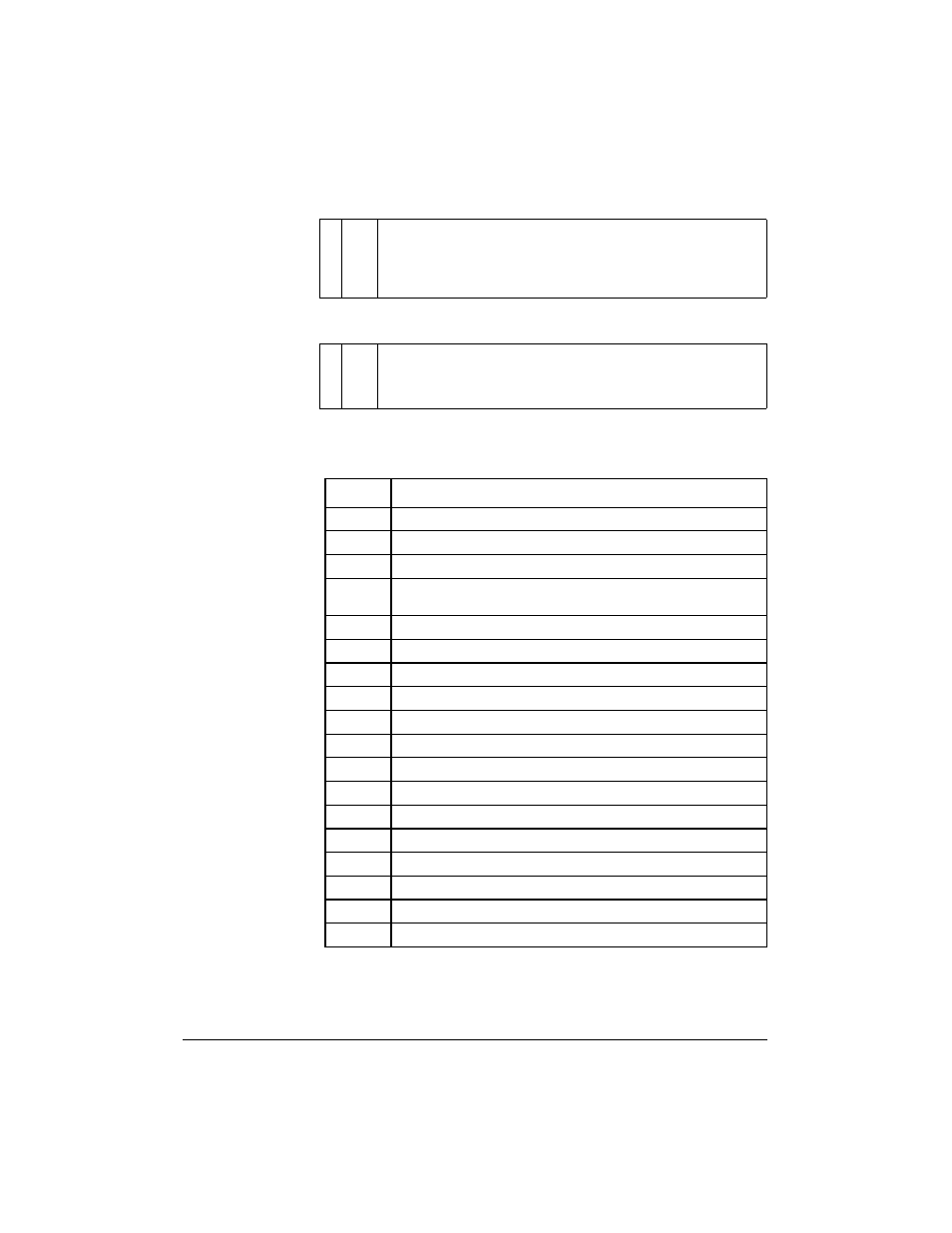

Table 2-11. PMC2 EventsÑMMCR0[26Ð31] Select Encodings

Encoding

Description

00 0000

Register holds current value.

00 0001

Counts processor cycles.

00 0010

Counts completed instructions. Does not include folded branches.

00 0011

Counts transitions from 0 to 1 of TBL bits speciÞed through

MMRC0[RTCSELECT]. 00 = 47, 01 = 51, 10 = 55, 11 = 63.

00 0100

Counts instructions dispatched. 0, 1, or 2 instructions per cycle.

00 0101

Counts L1 instruction cache misses.

00 0110

Counts ITLB misses.

00 0111

Counts L2 instruction misses.

00 1000

Counts branches predicted or resolved not taken.

00 1001

Counts MSR[PR] bit toggles.

00 1010

Counts times reserved load operations completed.

00 1011

Counts completed load and store instructions.

00 1100

Counts snoops to the L1 and the L2.

00 1101

Counts L1 cast-outs to the L2.

00 1110

Counts completed system unit instructions.

00 1111

Counts instruction fetch misses in the L1.

01 0000

Counts branches allowing out-of-order execution that resolved correctly.

All others

Reserved.