USL JSD-100 Manual User Manual

Page 39

Page 38

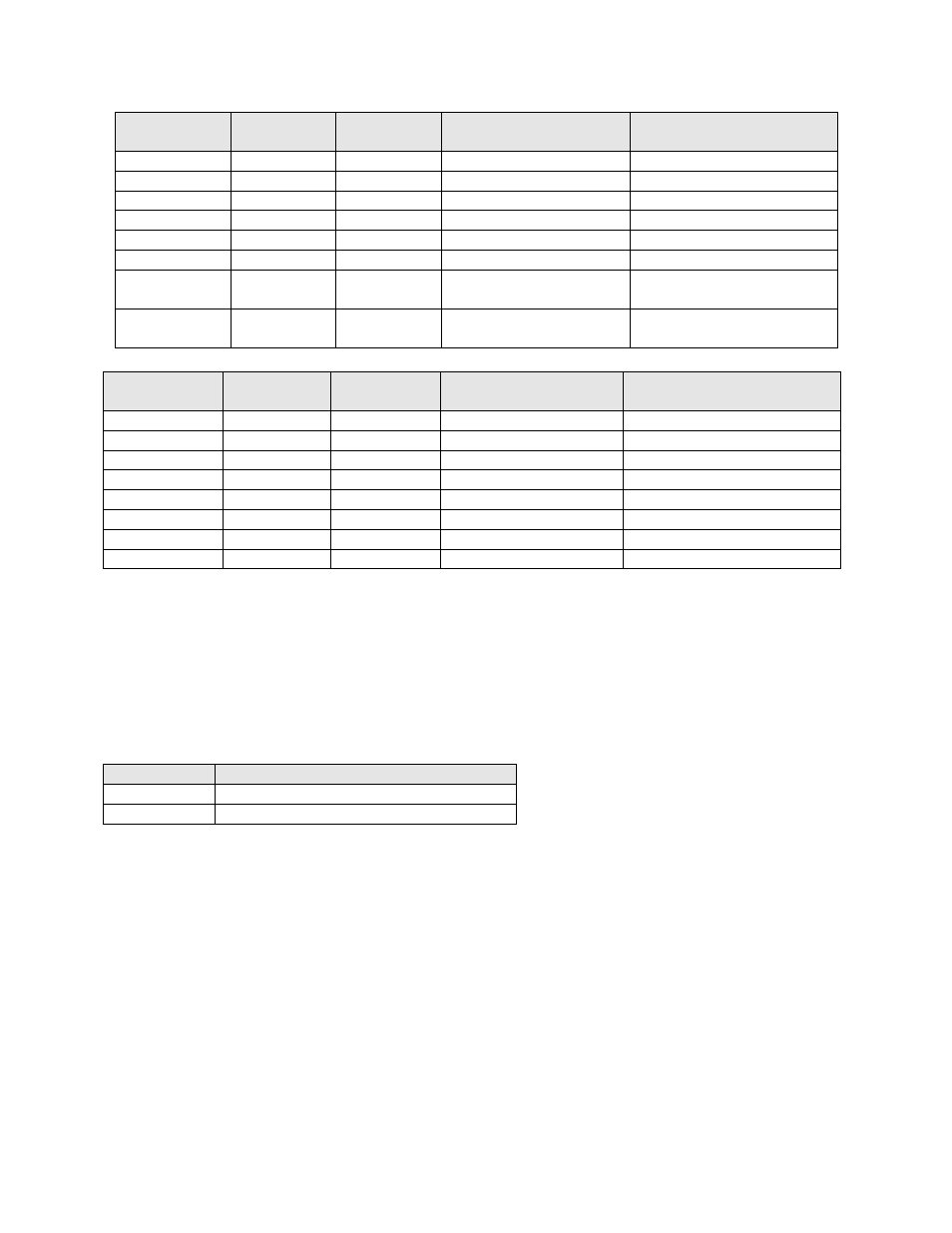

Full Range

Audio Channel

Biamp Audio

Channel

Triamp Audio

Channel

Phoenix Main Output Pins

(+, -, shield)

DB25M Monitor 1 Output

Pins (+, -, shield)

Left

Left Low

Left Low

1, 2, 3

2, 14, 1

Center

Center Low

Center Low

4, 5, 3

5, 17, 4

Right

Right Low

Right Low

6, 7, 8

8, 20, 7

LFE

LFE1

LFE1

9, 10, 8

25, 12, 13

Ls

Ls

Ls

11, 12, 13

23, 10, 22

Rs

Rs

Rs

14, 15, 13

24, 11, 9

Lrs/Lc (Lc only

in 13.1)

Lc Low

Lc Low

16, 17, 18

16, 3, 15

Rrs/Rc (Rc only

in 13.1)

Rc Low

Rc Low

19, 20, 18

19, 6, 18

Full Range

Audio Channel

Biamp Audio

Channel

Triamp Audio

Channel

Phoenix Optional Output

Pins (+, -, shield)

DB25F Monitor 2 Output Pins

(+, -), shield on pin 7

LFE2

Left High

Left High

1, 2, 3

13, 12

OUT 9

Lc High

Left Mid

4, 5, 3

14, 15

OUT 13

Unused

Center Mid

6, 7, 8

4, 18

OUT 14

Center High

Center High

9, 10, 8

5, 17

OUT 10

Rc High

Rc High

11, 12, 13

9, 22

LFE3

Right High

Right High

14, 15, 13

8, 20

Lrs

Lrs

Lrs

16, 17, 18

16, 3

Rrs

Rrs

Rrs

19, 20, 18

19, 6

HI/VI-N Outputs

The JSD-100 has balanced HI and VI-N outputs that can drive balanced or unbalanced loads. As with other outputs,

the use of twisted pair shielded cable is suggested whether the load is balanced or unbalanced. When driving an

unbalanced load, connect the “ – ” output of the JSD-100 to low side of the unbalanced input at the destination

end of the cable to minimize ground loop noise. The source of audio to drive the HI and VI-N outputs is

configurable on a per-format basis. The VI-N audio output is typically driven by AES input 16. The HI audio output

can be driven from AES inputs 7 or 15, or from a main audio mix. The USL supplied ferrite block should be clipped

on to the cables adjacent to the connectors to comply with FCC and CE emission requirements.

Audio Channel HI/VI-N Phoenix Connector Pins (+, -, shield)

HI

1, 2, 3

VI-N

4, 5, 3

Parallel Automation Interface

Pins 1 through 10 of the DB25F automation connector are “control” pins that accept contact closure or open

collector pulses to ground to select formats. On a format change, the corresponding pin is also pulsed low allowing

this interface to drive other equipment. Pulsing pin 11 low toggles the mute state. Pins 14 through 24 are “status”

pins. One of the pins 14 through 23 is pulled low continuously by the JSD-100 to indicate the selected format.

These pins could drive LEDs with a 470 ohm series resistor to provide a remote format indication. The JSD-100

pulls pin 24 low when the system is muted. Pins 1 through 11 are internally pulled up to +8.4V. They each source

400uA when grounded. A pin needs to be pulled below 2.6V for 10ms or more for the JSD-100 to recognize it as

low. On a format change, the JSD-100 pulls the appropriate pin low for 500ms. +5V at 100mA is available on pin 13

to drive external LEDs or relays. The individual control and status outputs can sink up to 150mA with an open

circuit voltage of +12VDC for inductive loads like relays or +24V for non-inductive loads (indicator lamps, etc.). Pin

12 is the “automation return.” Use this as the low side of switches and indicators instead of using chassis ground.

It is ground through a 10 ohm resistor to limit ground loop current. The USL supplied ferrite block should be

clipped on to the cables adjacent to the connectors to comply with FCC and CE emission requirements.