Rx - 8581 sa – Epson RX-8581JE User Manual

Page 10

RX

-

8581

SA

/

JE

/

NB

Page - 7

MQ372-02

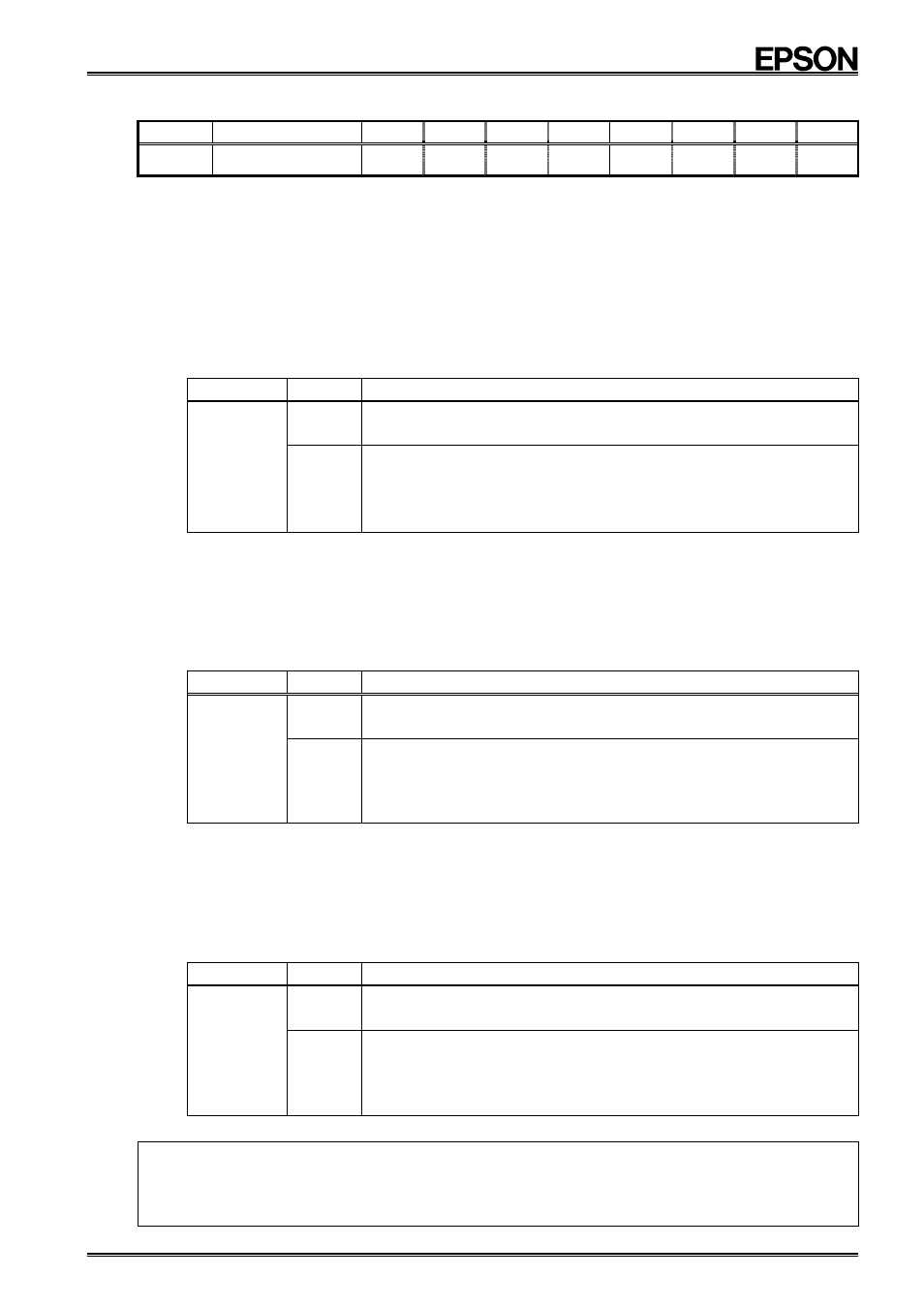

8.2.2. Control register (Reg F)

Address

Function

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2

bit 1

bit 0

Control Register

!

!

UIE

TIE

AIE

!

STOP

RESET

F

(Default)

(0)

(0)

(

−

)

(

−

)

(

−

)

(0)

(

−

)

(

−

)

∗

1)

The default value is the value that is read (or is set internally) after powering up from 0 V.

∗

2)

"o" indicates write-protected bits. A zero is always read from these bits.

∗

3)

"

−

" indicates no default value has been defined.

•

This register is used to control interrupt event output from the /INT pin and the stop/start status of clock and

calendar operations.

1) UIE (Update Interrupt Enable) bit

When a time update interrupt event is generated (when the UF bit value changes from "0" to "1"), this bit's value

specifies if an interrupt signal is generated (/INT status changes from Hi-Z to low) or is not generated (/INT

status remains Hi-Z).

When a "1"

is written to this bit, an interrupt signal is generated (/INT status changes from Hi-Z to low) when an

interrupt event is generated.

When a "0"

is written to this bit, no interrupt signal is generated when an interrupt event occurs.

UIE

Data Function

0

When a time update interrupt event occurs, an interrupt signal is not

generated or is canceled (/INT status changes from low to Hi-Z).

Write/Read

1

When a time update interrupt event occurs, an interrupt signal is generated

(/INT status changes from Hi-Z to low).

∗

When a time update interrupt event occurs, low-level output from the /INT

pin occurs only when

the value of the control register's UIE bit is "1". This /INT status is automatically cleared (/INT

status changes from low to Hi-Z) 7.8

ms after the interrupt occurs.

∗

For details, see "8.4. Time Update Interrupt Function".

2) TIE (Timer Interrupt Enable) bit

When a fixed-cycle timer interrupt event occurs (when the TF bit value changes from "0" to "1"), this bit's value

specifies if an interrupt signal is generated (/INT status changes from Hi-Z to low) or is not generated (/INT

status remains Hi-Z).

When a "1"

is written to this bit, an interrupt signal is generated (/INT status changes from Hi-Z to low) when an

interrupt event is generated.

When a "0"

is written to this bit, no interrupt signal is generated when an interrupt event occurs.

TIE

Data Function

0

When a fixed-cycle timer interrupt event occurs, an interrupt signal is not

generated or is canceled (/INT status changes from low to Hi-Z).

Write/Read

1

When a fixed-cycle timer interrupt event occurs, an interrupt signal is

generated (/INT status changes from Hi-Z to low).

*

When a fixed-cycle timer interrupt event has been generated low-level output from the /INT pin

occurs only when the value of the control register's TIE bit is "1". Up to 7.8 ms after the interrupt

occurs, the /INT status is automatically cleared (/INT status changes from low to Hi-Z)

.

∗

For details, see "8.3. Fixed-cycle Timer Interrupt Function".

3) AIE (Alarm Interrupt Enable) bit

When an alarm timer interrupt event occurs (when the AF bit value changes from "0" to "1"), this bit's value

specifies if an interrupt signal is generated (/INT status changes from Hi-Z to low) or is not generated (/INT

status remains Hi-Z).

When a "1"

is written to this bit, an interrupt signal is generated (/INT status changes from Hi-Z to low) when an

interrupt event is generated.

When a "0"

is written to this bit, no interrupt signal is generated when an interrupt event occurs.

AIE

Data

Function

0

When an alarm interrupt event occurs, an interrupt signal is not generated

or is canceled (/INT status changes from low to Hi-Z).

Write/Read

1

When an alarm interrupt event occurs, an interrupt signal is generated

(/INT status changes from Hi-Z to low).

∗

When an alarm interrupt event has been generated low-level output from the /INT pin occurs

only when the value of the control register's AIE bit is "1". This setting is retained until the AF bit

value is cleared to zero. (No automatic cancellation)

∗

For details, see "8.5. Alarm Interrupt Function".

[Caution]

(1) The /INT pin is a shared interrupt output pin for three types of interrupts. It outputs the OR'ed result of these interrupt outputs.

When an interrupt has occurred (when the /INT pin is at low level), the UF,

TF,

read AF flags to determine which flag has a value of "1"

(this indicates which type of interrupt event has occurred).

(2) To keep the /INT pin from changing to low level, write "0" to the UIE,

TIE,

and AIE bits. To check whether an event has occurred without

outputting any interrupts via the /INT pin, use software to monitor the value of the UF,

TF,

and AF interrupt flags.