Otp rom – ELAN Home Systems EM78P458 User Manual

Page 20

EM78P458/459

OTP ROM

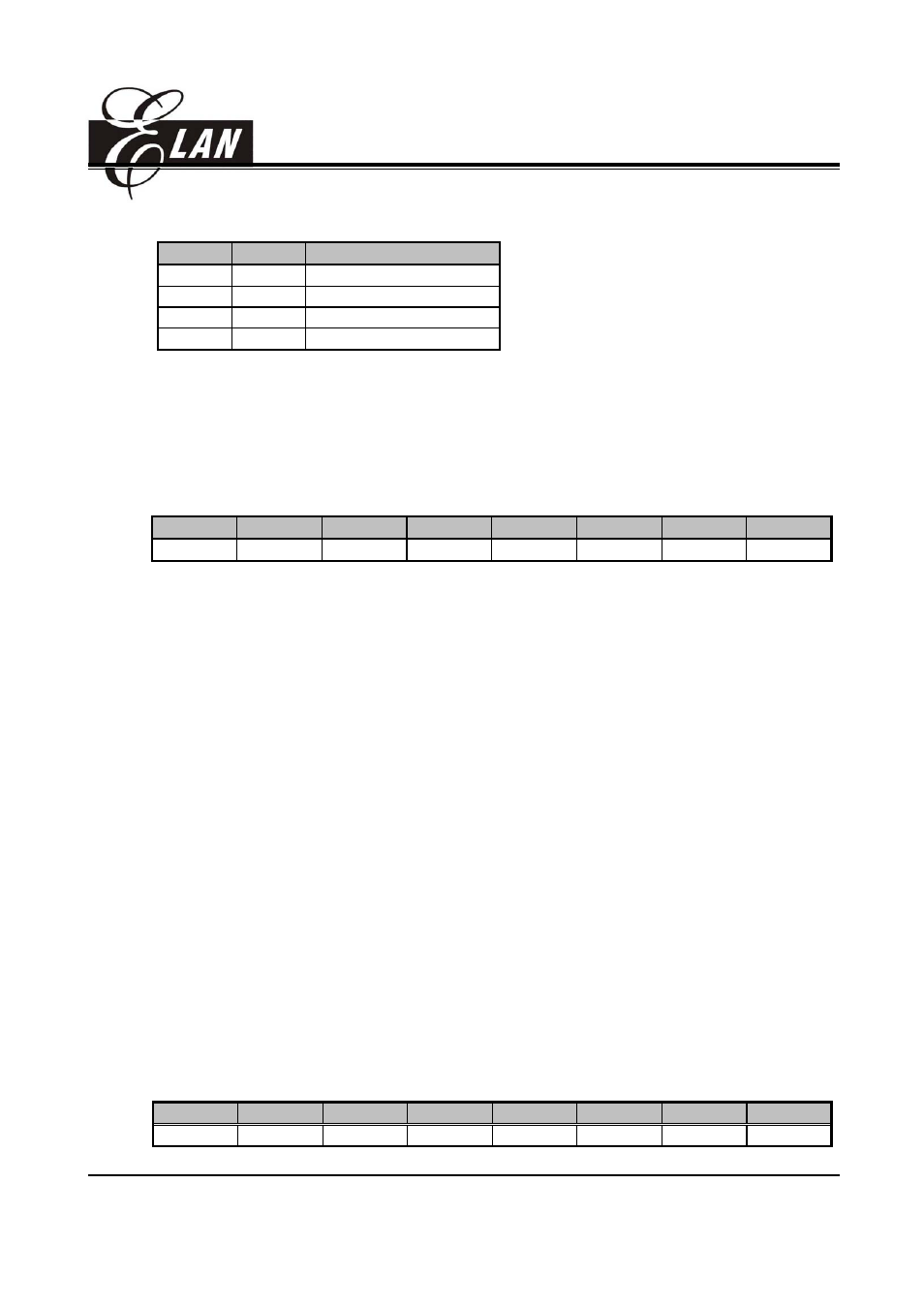

• Bit 1 : Bit 0 ( T1P1:T1P0 ): TMR1 clock prescale option bits.

T1P1

T1P0

Prescale

0 0

1:2(Default)

0 1

1:8

1 0

1:32

1 1

1:64

12. IOC61 ( DT1L: the Least Significant Byte ( Bit 7 ~ Bit 0) of Duty Cycle of

PWM1 )

A specified value keeps the output of PWM1 to stay at high until the value matches with TMR1.

13. IOC71 ( DT1H: the Most Significant Byte ( Bit 1 ~ Bit 0 ) of Duty Cycle of

PWM1 )

7

6

5

4

3

2

1

0

CALI1 SIGN1 VOF1[2]

VOF1[1]

VOF1[0] - PWM1[9]

PWM1[8]

• Bit 7 (CALI1): Calibration enable bit

0 = Calibration disable;

1 = Calibration enable.

• Bit 6 (SIGN1): Polarity bit of offset voltage

0 = Negative voltage;

1 = Positive voltage.

• Bit 5:Bit 3 (VOF1[2]:VOF1[0]): Offset voltage bits.

• Bit 1:Bit 0 (PWM1[9]:PWM1[8]): The Most Significant Byte of PWM1 Duty Cycle

A specified value keeps the PWM1 output to stay at high until the value matches with TMR1.

14. IOC81 ( PRD1: Period of PWM1 ):

The content of IOC81 is a period (time base) of PWM1. The frequency of PWM1 is the reverse of the

period.

15. IOC91 ( DT2L: the Least Significant Byte ( Bit 7 ~ Bit 0 ) of Duty Cycle of

PWM2 )

A specified value keeps the of PWM1 output to stay at high until the value matches with TMR2.

16. IOCA1 ( DT2H: the Most Significant Byte ( Bit 1 ~ Bit 0 ) of Duty Cycle of

PWM2 )

7

6

5

4

3

2

1

0

CALI2 SIGN2 VOF2[2]

VOF2[1]

VOF2[0] - PWM2[9]

PWM2[8]

This specification is subject to change without prior notice. 07.01.2003 (V1.3)

20

• Bit 7 (CALI2): Calibration enable bit