Rx − 8801 sa / je – Epson RX-8801SA/JE User Manual

Page 13

RX

− 8801 SA / JE

Page - 10

ETM26E-03

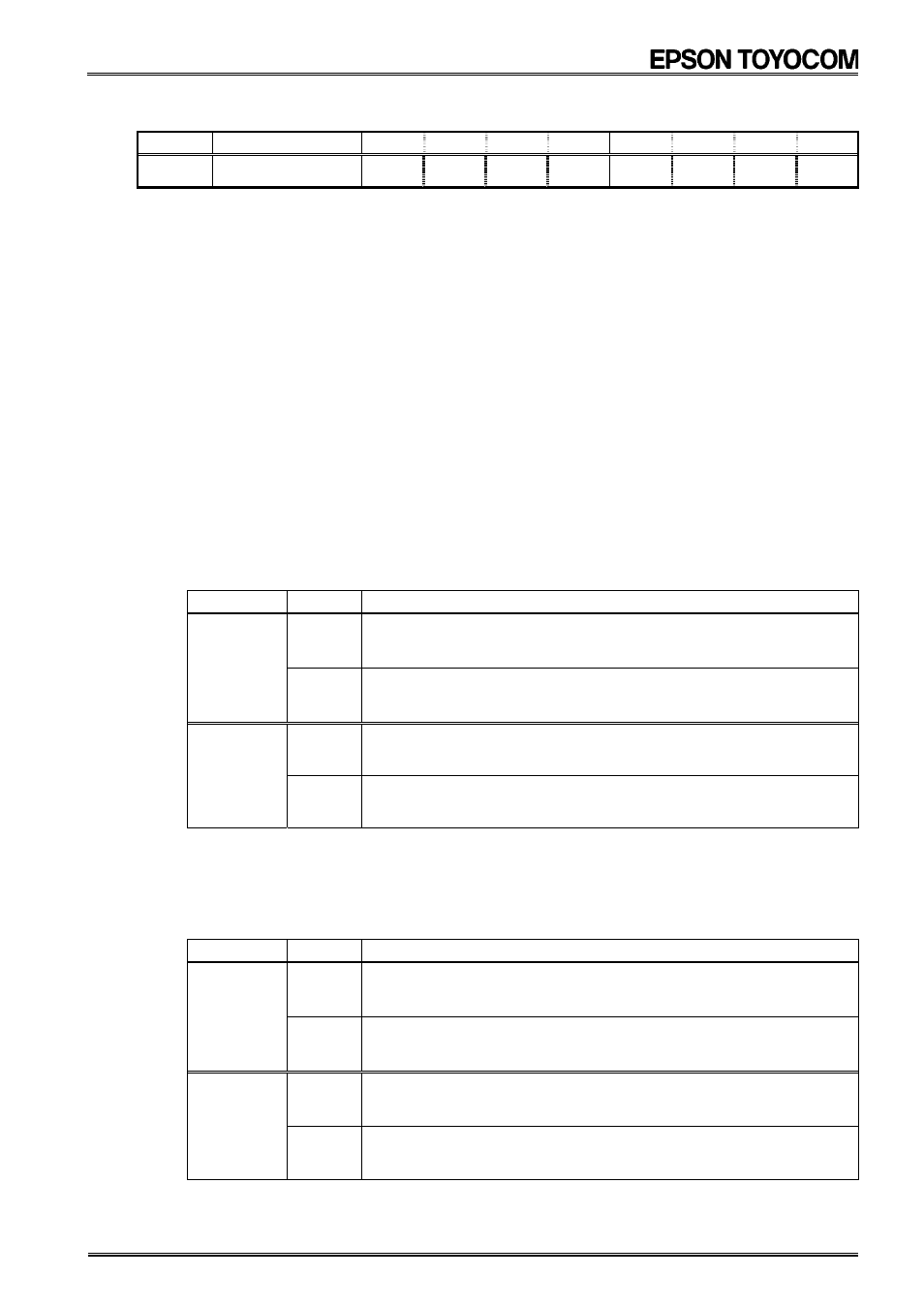

8.2.3. Flag register (Reg-E)

Address

Function

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2

bit 1

bit 0

Flag register

{

{

UF

TF

AF

{

VLF

VDET

E

(Default)

(0)

(0)

(

−)

(

−)

(

−)

(0)

(1)

(1)

∗1)

The default value is the value that is read (or is set internally) after powering up from 0 V.

∗2)

"o" indicates write-protected bits. A zero is always read from these bits.

∗3)

"−" indicates a default value is undefined.

• This register is used to detect the occurrence of various interrupt events and reliability problems in internal data.

1) UF ( Update Flag ) bit

If set to "0" beforehand, this flag bit's value changes from "0" to 1" when a time update interrupt event has

occurred. Once this flag bit's value is "1", its value is retained until a "0" is written to it.

∗

For details, see "8.4. Time Update Interrupt Function".

2) TF ( Timer Flag ) bit

If set to "0" beforehand, this flag bit's value changes from "0" to 1" when a fixed-cycle timer interrupt event has

occurred. Once this flag bit's value is "1", its value is retained until a "0" is written to it.

∗

For details, see "8.3. Fixed-cycle Timer Interrupt Function".

3) AF ( Alarm Flag ) bit

If set to "0" beforehand, this flag bit's value changes from "0" to 1" when an alarm interrupt event has occurred.

Once this flag bit's value is "1", its value is retained until a "0" is written to it.

∗

For details, see "8.5. Alarm Interrupt Function".

4) VLF ( Voltage Low Flag ) bit

This flag bit indicates the retained status of clock operations or internal data. Its value changes from "0" to "1"

when data loss occurs, such as due to a supply voltage drop. Once this flag bit's value is "1", its value is retained

until a "0" is written to it.

When after powering up from 0 V this bit's value is "1" .

VLF

Data Description

0

The VLF bit is cleared to zero to prepare for the next status detection.

Write

1

This bit is invalid after a "1" has been written to it.

0

Data loss is not detected.

Read

1

Data loss is detected. All registers must be initialized.

( This setting is retained until a "zero" is written to this bit. )

5) VDET ( Voltage Detection Flag ) bit

This flag bit indicates the status of temperature compensation. Its value changes from "0" to "1" when stop the

temperature compensation, such as due to a supply voltage drop. Once this flag bit's value is "1", its value is

retained until a "0" is written to it.

When after powering up from 0 V this bit's value is "1" .

VDET

Data Description

0

The VDET bit is cleared to zero to prepare for the next low voltage detection.

Write

1

The write access of "1" to this bit is invalid.

0

Temperature compensation is normal.

Read

1

Temperature compensation is stop detected.