Rx − 8801 sa / je – Epson RX-8801SA/JE User Manual

Page 11

RX

− 8801 SA / JE

Page - 8

ETM26E-03

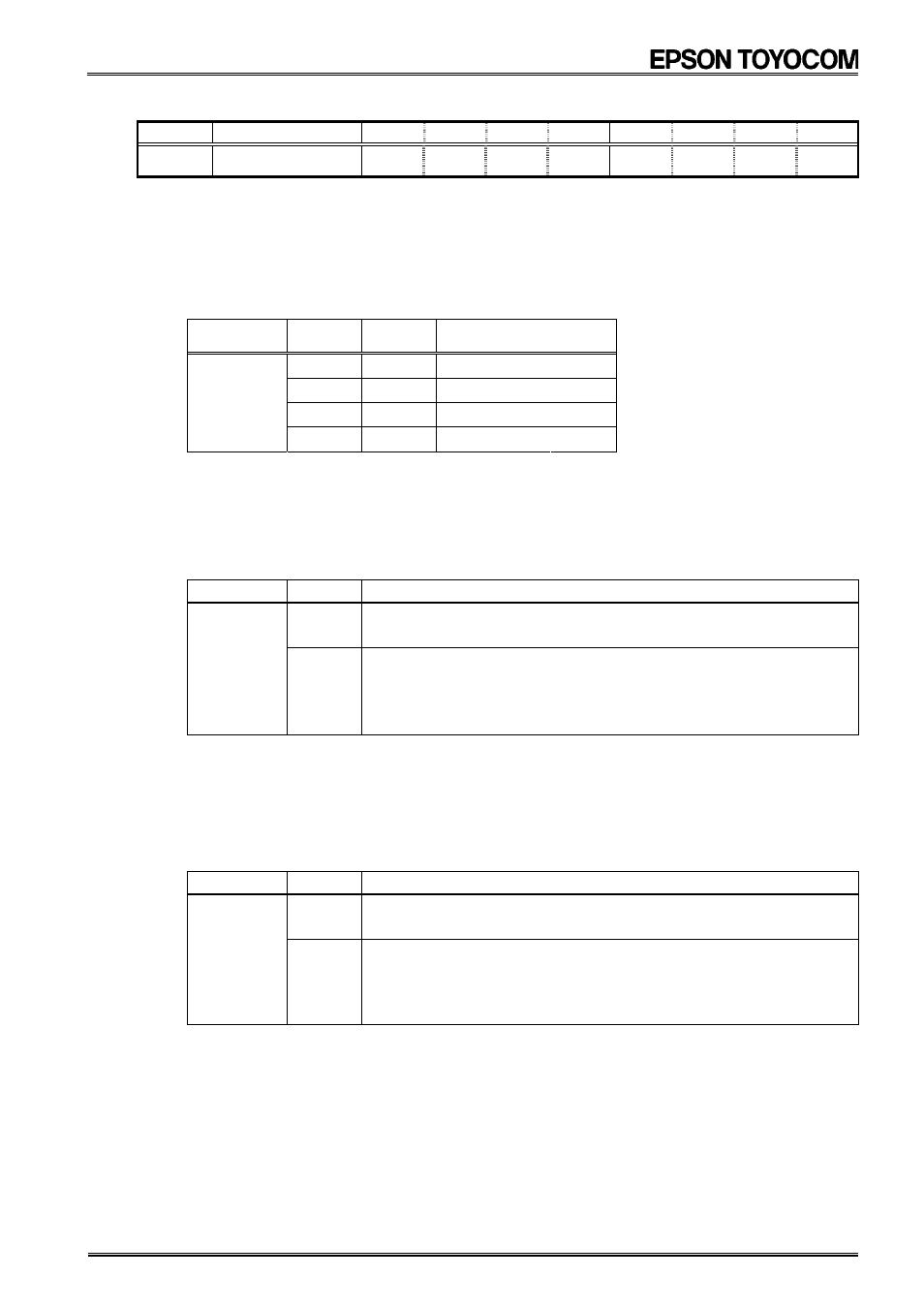

8.2.2. Control register (Reg F)

Address

Function

bit 7

bit 6

bit 5

bit 4

bit 3

bit 2

bit 1

bit 0

Control Register

CSEL1

CSEL0

UIE

TIE

AIE

{

{

RESET

F

(Default)

(0)

(1)

(

−)

(

−)

(

−)

(0)

(0)

(

−)

∗1)

The default value is the value that is read (or is set internally) after powering up from 0 V.

∗2)

"o" indicates write-protected bits. A zero is always read from these bits.

∗3)

"−" indicates no default value has been defined.

• This register is used to control interrupt event output from the /INT pin and the stop/start status of clock and

calendar operations.

1) CSEL0,1 ( Compensation interval Select 0, 1 ) bits

The combination of these two bits is used to set the temperature compensation interval.

CSEL0,1

CSEL1

(bit 7)

CSEL0

(bit 6)

Compensation interval

0 0 0.5

s

0 1 2.0

s

∗ Default

1 0 10

s

Write/Read

1 1 30

s

2) UIE ( Update Interrupt Enable ) bit

When a time update interrupt event is generated (when the UF bit value changes from "0" to "1"), this bit's value

specifies if an interrupt signal is generated (/INT status changes from Hi-Z to low) or is not generated (/INT status

remains Hi-Z).

When a "1"

is written to this bit, an interrupt signal is generated (/INT status changes from Hi-Z to low) when an

interrupt event is generated.

When a "0"

is written to this bit, no interrupt signal is generated when an interrupt event occurs.

UIE

Data Function

0

When a time update interrupt event occurs, an interrupt signal is not

generated or is canceled (/INT status changes from low to Hi-Z).

Write/Read

1

When a time update interrupt event occurs, an interrupt signal is generated

(/INT status changes from Hi-Z to low).

∗

When a time update interrupt event occurs, low-level output from the /INT

pin occurs only when

the value of the control register's UIE bit is "1". This /INT status is automatically cleared (/INT

status changes from low to Hi-Z) 7.8

ms after the interrupt occurs.

2) TIE ( Timer Interrupt Enable ) bit

When a fixed-cycle timer interrupt event occurs (when the TF bit value changes from "0" to "1"), this bit's value

specifies if an interrupt signal is generated (/INT status changes from Hi-Z to low) or is not generated (/INT status

remains Hi-Z).

When a "1"

is written to this bit, an interrupt signal is generated (/INT status changes from Hi-Z to low) when an

interrupt event is generated.

When a "0"

is written to this bit, no interrupt signal is generated when an interrupt event occurs.

TIE

Data Function

0

When a fixed-cycle timer interrupt event occurs, an interrupt signal is not

generated or is canceled (/INT status changes from low to Hi-Z).

Write/Read

1

When a fixed-cycle timer interrupt event occurs, an interrupt signal is

generated (/INT status changes from Hi-Z to low).

*

When a fixed-cycle timer interrupt event has been generated low-level output from the /INT pin

occurs only when the value of the control register's TIE bit is "1". Up to 7.8 ms after the interrupt

occurs, the /INT status is automatically cleared (/INT status changes from low to Hi-Z)

.