And-tft-64pa-dhb – Purdy AND-TFT-64PA-DHB User Manual

Page 4

AND-TFT-64PA-DHB

Purdy Electronics Corporation • 720 Palomar Avenue • Sunnyvale, CA 94085

4

Tel: 408.523.8200 • Fax: 408.733.1287 • [email protected] • www.purdyelectronics.com

7-28-99

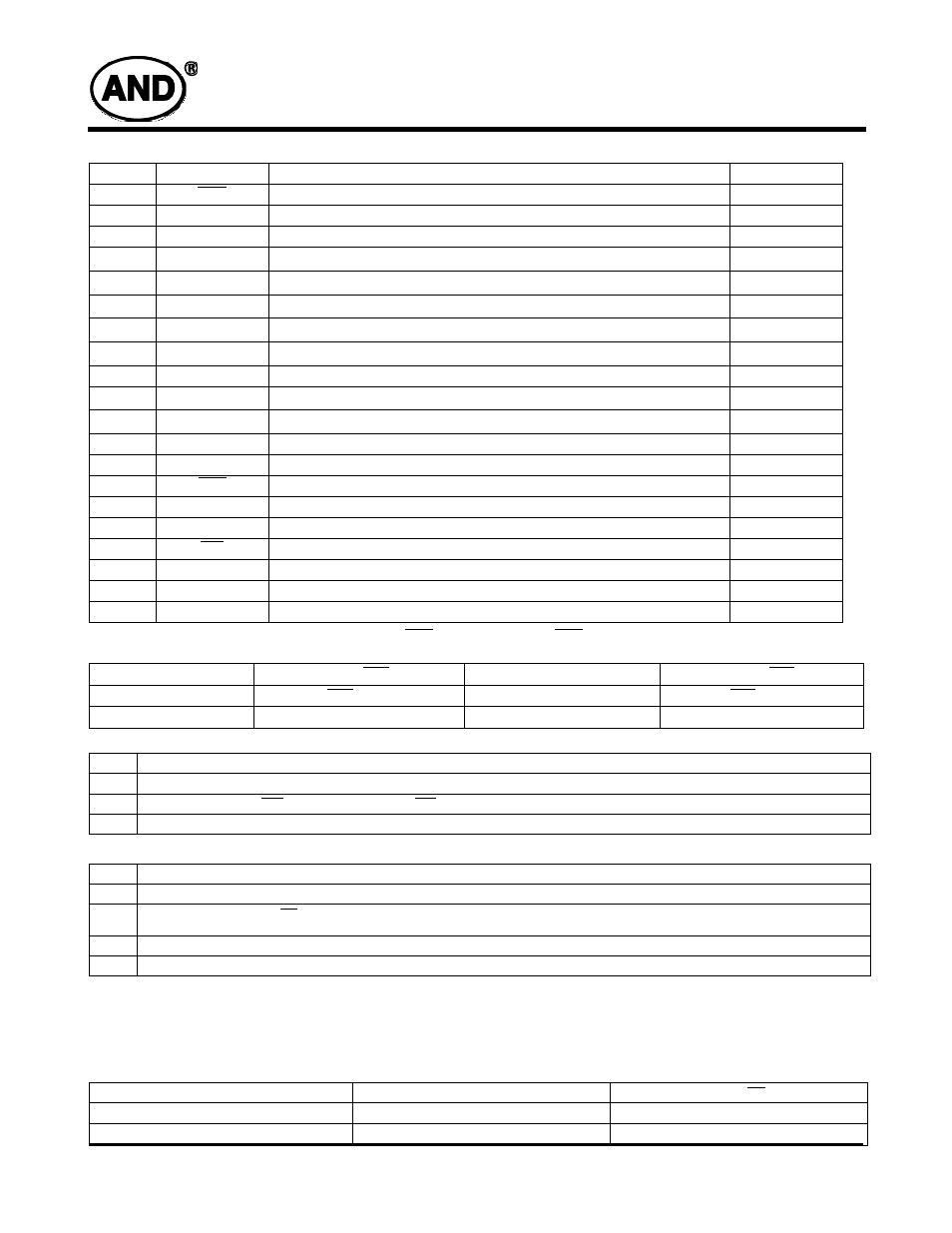

Interface Pin Assignment Connector 1: Connector 1 (28 Pins) (Elco) 6200-500-28-800

1. Pin 13 (CLKC) can select the function of pin 1 (HSY), 3 (CSY), and 14 (VSY) as follows:

2. CKC = High:

3. CKC = Low:

4. If there is any question about CKC = 0, please contact Purdy Electronics.

5. V

GH

TYP._+17V ; V

GL

TYP._-15V ; V

DD

TYP._+5V ; V

CC

TYP._+5V

6. The frequency of PSI is 15.75 KHz.

7. Pin 16 (COMPS) can select composite sync. mode OR sync. separate mode

Pin No.

Symbol

Function

I/O

1

HSY

Horizontal Sync. Input / Output

Input/Output

2

POLC

Video Polarity Alternating Signal

Output

3

CSY/MCLK

Composite Sync. Signal / Mclk Signal

Input

4

V

GH

Gate on voltage

Input

5

V

GL

Gate off voltage (alternate every 1-H)

Input

6

V

B

Video Input B

Input

7

V

R

Video Input R

Input

8

V

G

Video Input G

Input

9

GND

Ground

Input

10

V

DD

Digital power input

Input

11

V

CC

Logic power for gate driver

Input

12

GND

Ground

Input

13*

CLKC

Control pin for select I/O signal

Input/Output

14

VSY

Vertical Sync. Input / Output

Input/Output

15

PSI

Synchronize pulse for external clock

Input

16

COMPS

Select composite sync. mode & sync. separate mode

Input

17

VIY

Vertical sync. input pin for sync. separate mode

Input

18

U/D

Up/Down control for gate driver

Input

19

R/L

Left/Right control for gate driver

Input

20

NP

NTSC/PAL Input

Input

CKC

Pin 1 (HSY)

Pin 3 (CSY)

Pin 14 (VSY)

Hi

HSY output

CSY input

VSY output

Low

External Horizontal Sync. input

External Clock input

External Vertical Sync input

a. If CKC = 1, the phase lock loop (pll) is adopted in the LCd module.

b. Inputs CSY, the controller of LCD module will separate the Vertical Sync and Horizontal Synch from CSY.

c. Out put Horizontal Sync (HSY , Pin 1) and Vertical Sync (VSY , Pin 14.)

d. The internal detect will detect Vertical Sync to reset the vertical counter.

a. If CKC = 0, the phase lock loop (PLL) is not adopted in the LCD module.

b. If CKC = 0, the external clock input frequency of Pin 3 is 6.4 MHz.

c.

Input external Vertical Sync. (VIY , Pin 17) and Horizontal Sync. (Pin1) to synchronize the LCD module. External Horizontal Sync and External Vertical

Sync. input pulse can be high going or low going.

d. The pulse width of external Horizontal SYnc. input is 4.7

µ

s ±2

µ

s. The pulse width of external Vertical Sync. input is 2H~4H.

e. The pulse length of external input Vertical Sync. of system is 262H ±4H.

Pin 16 (COMPS)

Pin 3 (CSY)

Pin 17 (VIY)

Hi

CSY (Positive Edge)

NC

Low

H

sync

(Negative Edge)

V

sync

(Negative Edge)